XM25QU128B 128Mb 1.8V SERIAL FLASH MEMORY WITH 133MHZ MULTI I/O SPI & QUAD I/O QPI DTR INTERFACE

XMC(武汉芯新) XM25QU128BHIQ芯片特点:

一、接口与容量

容量:128Mbit/16MB

页面大小:256 字节 / 可编程页

接口:标准 SPI、Fast、Dual、Dual I/O、Quad、Quad I/O、SPI DTR、Dual I/O DTR、Quad I/O DTR、QPI

支持协议:SFDP(串行闪存可发现参数)

二、高性能特性

正常读取:50MHz;快速读取:133MHz

QPI 等效频率:532MHz

DTR 双传输速率:最高 66MHz

可选 dummy 周期、驱动强度可调

支持 SPI 模式 0 & 3

擦写寿命:≥10 万次

数据保存:>20 年

三、灵活架构

支持芯片擦除、扇区 / 块擦除:4KB / 32KB / 64KB

每页编程:1~256 字节

支持编程 / 擦除挂起与恢复

四、高效读写模式

低指令开销操作

连续读取:8/16/32/64 字节突发环绕

突发长度可选

QPI 模式降低指令开销

支持自动启动(AutoBoot)

五、低功耗与宽温

工作电压:1.65V–1.95V

工作读取电流:10mA

待机电流:8μA

深度掉电电流:1μA

工业温度:-40°C ~ +85°C

六、安全保护

软件 & 硬件写保护

电源锁定保护

4×256 字节专用安全区域,带 OTP 用户可锁定位

每颗芯片 128bit 唯一 ID(需工厂获取)

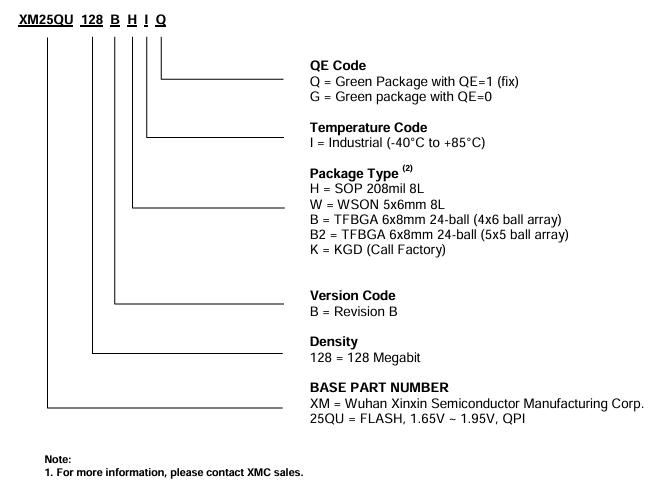

封装:

H = SOP 208mil 8L

W = WSON 5x6mm 8L

B = TFBGA 6x8mm 24-ball (4x6 ball array)

B2 = TFBGA 6x8mm 24-ball (5x5 ball array)

K = KGD (Call Factory)

XM25QU128CHIQ芯片说明:

一、概述

XM25QU128B 串行闪存采用精简引脚封装,提供兼具高灵活性与高性能的通用存储解决方案。XMC 这款工业标准串行接口闪存,适用于对空间受限、引脚数少、低功耗有要求的系统。器件通过 4 线 SPI 接口访问,包括串行数据输入(SI)、串行数据输出(SO)、串行时钟(SCK)和片选使能(CE#)引脚,这些引脚也可配置为多 I/O 功能(详见引脚说明)。

器件支持双通道、四通道 I/O,以及标准 SPI、双通道输出、四通道输出 SPI。时钟频率最高可达 133MHz,等效时钟频率最高可达 532MHz(133MHz × 4),对应数据吞吐率为 66MB/s。XM25Qx 系列闪存新增 DTR(双倍传输速率) 指令支持,可在时钟上下沿同时传输地址与读取数据。此类传输速率可超越 16 位并行闪存,实现高效存储访问,支持 XIP(片内执行) 功能。

存储器阵列按 256 字节可编程页组织。该系列支持页编程模式,单条指令可编程 1~256 字节数据。QPI(四路外设接口) 支持 2 周期指令,进一步缩短指令耗时。可按 4KB 扇区、32KB 块、64KB 块 或整片进行擦除。统一的扇区与块架构带来高度灵活性,使器件可广泛用于各类对数据保持可靠性有要求的应用。

二、术语表

标准 SPI

采用 4 线 SPI 接口:串行数据输入(SI)、串行数据输出(SO)、串行时钟(SCK)、片选使能(CE#)。指令通过 SI 引脚,在时钟上升沿输入器件,用于编码指令、地址或写入数据;SO 引脚用于读取数据或查询器件状态。本器件支持 SPI 总线工作模式 (0,0) 和 (1,1)。

多 I/O SPI

多 I/O 操作采用增强型 SPI 协议,使器件支持:双通道输出、双通道输入输出、四通道输出、四通道输入输出。在 SPI 模式下执行这些指令,可使读、写操作带宽提升 2 倍或 4 倍。

QPI

仅通过 进入 QPI(35h) 指令,将器件从标准 / 双通道 / 四通道 SPI 模式切换至 QPI 模式后,方可支持 QPI 操作。传统 SPI 协议中,8 位指令码仅能通过 SI 引脚,在 8 个时钟周期内移入器件;QPI 模式则利用全部 4 路 I/O 引脚输入指令码,仅需 2 个时钟周期,可显著降低 SPI 指令开销,提升系统性能。同一时刻仅 QPI 模式 或 SPI / 双通道 / 四通道模式有效。无论状态寄存器中非易失性四通道使能(QE)位状态如何,均可使用进入 QPI(35h) 和退出 QPI(F5h) 指令在两种模式间切换。上电复位或硬件 / 软件复位后,器件将恢复为标准 SPI 模式。QPI 模式下:SI → 双向 I/O0,SO → I/O1,WP# → I/O2,HOLD# → I/O3。

DTR

除 SPI 与 QPI 功能外,器件还支持快速读取 DTR 操作。DTR 可在更低时钟频率下实现高数据吞吐。快速读取 DTR 在时钟上升沿与下降沿同时输入地址、输出数据,使输入输出周期减半。