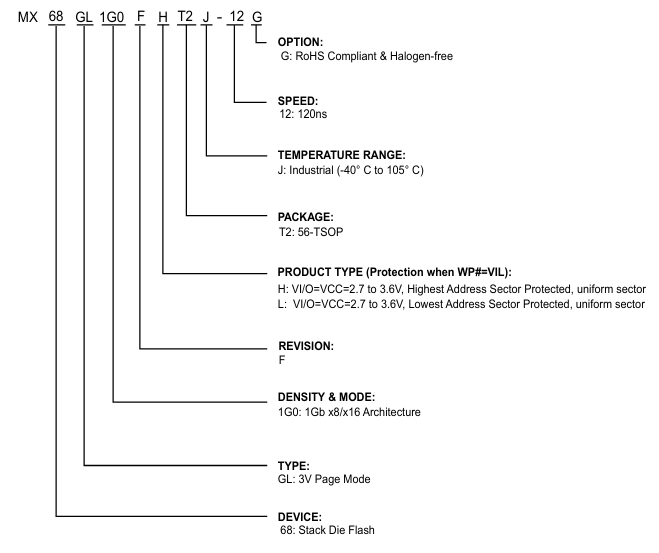

MX68GL1G0F - J Grade DATASHEET SINGLE VOLTAGE 3V ONLY FLASH MEMORY

MXIC(旺宏电子)MX68GL1G0FLT2J-12G NOR Flash芯片型号的主要功能:

1. 特性

通用特性

读取、擦除与编程操作电压:2.7V~3.6V

可切换字节 / 字模式:134217728×8 位 / 67108864×16 位

64KW/128KB 均匀扇区架构,共 1024 个等大小扇区

16 字节 / 8 字页面读取缓存

64 字节 / 32 字写入缓存

额外 128 字安全扇区:出厂锁定且具备唯一标识,支持用户锁定

高级扇区保护功能(硬件保护与密码保护)

兼容 JEDEC 标准:引脚排布与软件协议兼容单电源闪存

性能参数

高性能

快速访问时间:MX68GL1G0F H/L 型为 120ns

页面访问时间:MX68GL1G0F H/L 型为 30ns

快速编程时间:11μs / 字

快速擦除时间:0.6s / 扇区

低功耗

读取工作电流:5MHz 频率下典型值 20mA

待机电流:典型值 120μA

擦写 / 编程循环寿命:最少 10 万次

数据保存时间:20 年

软件特性

编程 / 擦除挂起与编程 / 擦除恢复功能

状态反馈:通过数据查询(Data# Polling)与翻转位检测编程、擦除操作完成状态

支持通用闪存接口(CFI)

硬件特性

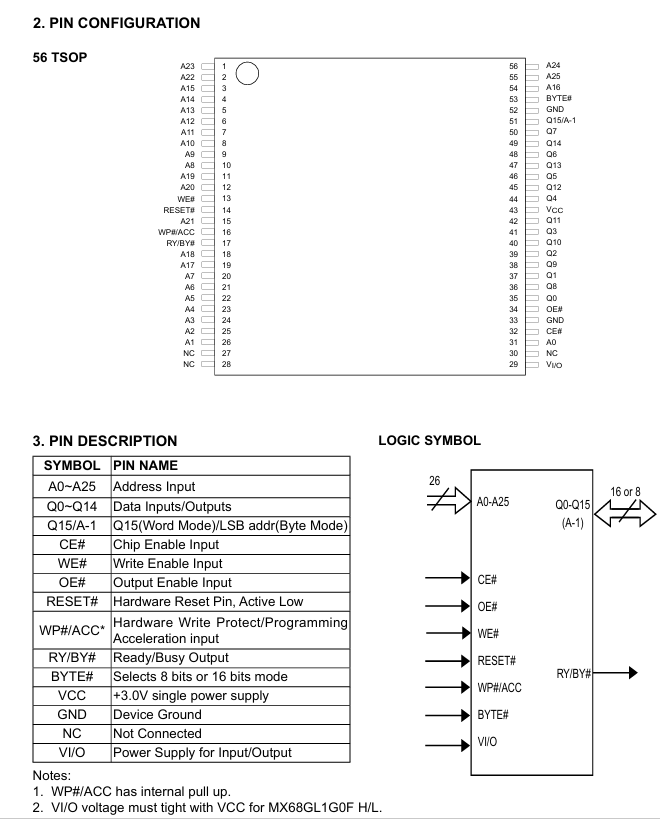

就绪 / 忙(RY/BY#)输出引脚:通过硬件方式检测编程与擦除操作完成状态

硬件复位(RESET#)输入引脚:通过硬件方式将内部状态机复位至读取模式

WP#/ACC 输入引脚:硬件写保护引脚,同时提供加速编程功能

封装形式

T2:56-TSOP

所有器件均符合 RoHS 标准且无卤素

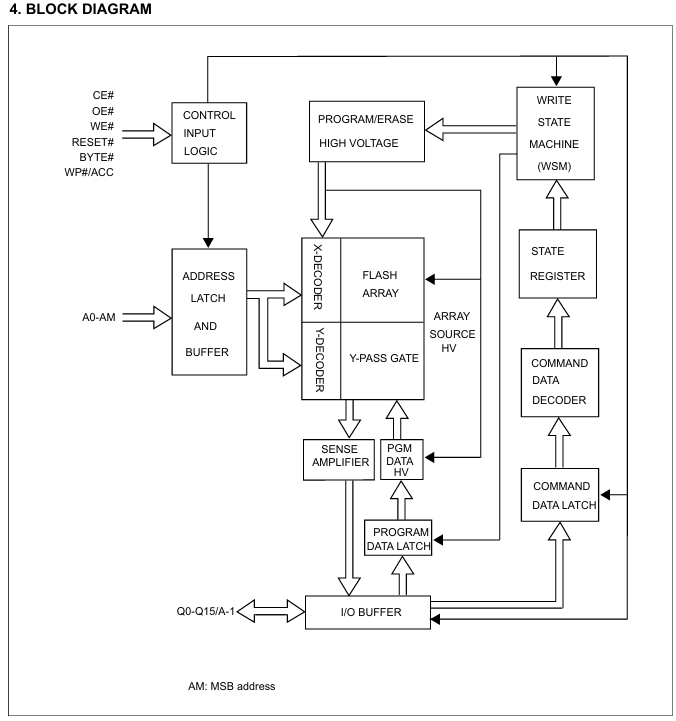

“功能框图” 展示了该器件的简化架构。框图中的每个模块对应实际芯片中用于对存储阵列进行访问、擦除、编程和读取操作的一个或多个电路单元。

“控制输入逻辑”模块接收片选使能 CE#、输出使能 OE#、写使能 WE#、复位 RESET#、字节模式 BYTE# 以及写保护 / 加速 WP#/ACC 等输入引脚信号。该模块根据输入引脚生成内部时序控制信号,并输出至“地址锁存与缓冲器”,对外部地址引脚 A0~AM 进行锁存。内部地址由此模块输出至由X 译码器、Y 译码器、Y 传输门和闪存阵列组成的主阵列及译码单元。

X 译码器对闪存阵列的字线进行译码,Y 译码器则对闪存阵列的位线进行译码。位线通过 Y 传输门选择性地与 **“灵敏放大器”和“编程数据高压模块”电气连接。灵敏放大器用于读出闪存存储内容,而“编程数据高压模块”** 则在编程操作期间有选择地向位线施加高压。

“I/O 缓冲器”控制 Q0~Q15/A-1 焊盘的数据输入与输出。读取操作时,I/O 缓冲器从灵敏放大器获取数据,并驱动相应输出焊盘。在编程指令的最后一个周期,I/O 缓冲器将 Q0~Q15/A-1 上的数据传输至“编程数据锁存器”,该锁存器控制 **“编程数据高压模块”** 中的高压驱动电路,根据用户输入数据格式对字或字节单元中的存储位执行选择性编程。

“编程 / 擦除高压生成”模块包含产生并向 X 译码器、闪存阵列及编程数据高压模块提供所需高压的电路。逻辑控制模块由“写状态机(WSM)”、“状态寄存器”、**“指令数据译码器”和“指令数据锁存器”** 组成。

当用户通过翻转 WE# 引脚发出指令时,Q0~Q15/A-1 上的指令将被锁存至指令数据锁存器,并由指令数据译码器进行译码。状态寄存器接收指令并记录器件当前工作状态。写状态机根据当前指令状态,通过控制框图中的各个模块,执行内部编程或擦除算法。

阵列架构

主闪存阵列可配置为字节模式(×8)或字模式(×16)。地址范围及对应扇区地址的详细信息见表 1。