MX25L12873F 3V 128M-BIT [x 1/x 2/x 4] CMOS MXSMIO™(SERIAL MULTI I/O) FLASH MEMORY

MXIC(旺宏电子)MX25L12873FZNI-10G Serial NOR Flash芯片特点:

1. 产品特性

通用特性

支持串行外设接口 —— 模式 0 与模式 3

单电源供电运行

读取、擦除及编程操作电压范围:2.7~3.6 伏

存储容量 128Mb:支持三种存储位宽架构,分别为 134,217,728×1 比特、67,108,864×2 比特(双 I/O 模式)、33,554,432×4 比特(四 I/O 模式)

协议支持

单 I/O、双 I/O 及四 I/O 协议

闩锁保护能力:在 - 1V 至 Vcc+1V 电压范围内,可承受 100mA 电流冲击

SPI 模式快速读取功能

全协议下支持最高 133MHz 时钟频率

支持快速读取、2 线读取、双 I/O 读取、4 线读取、四 I/O 读取指令

快速读取操作的虚拟周期数可配置

默认启用四 I/O 模式(QE 位 = 1),且该配置不可修改

支持四外设接口(QPI)

扇区与块划分:支持 4KB 等容量扇区、32KB 等容量块或 64KB 等容量块

任意块均可独立擦除

编程特性

配备 256 字节页缓冲器

支持四 I/O 页编程指令(4PP),提升编程性能

典型擦除 / 编程循环次数:100,000 次

数据保存期限:20 年

软件特性

输入数据格式

1 字节指令编码

高级安全特性

块锁定保护:通过 BP0-BP3 及 T/B 状态位定义受保护区域大小,防止该区域被执行编程与擦除指令

高级扇区保护功能(固化保护与密码保护)

额外 4K 比特一次性可编程(OTP)安全存储区

内置唯一标识符

支持工厂锁定(可识别)及客户自主锁定

指令复位功能

编程 / 擦除暂停与恢复操作

电子身份识别

遵循 JEDEC 标准:1 字节制造商 ID 与 2 字节器件 ID

RES 指令:读取 1 字节器件 ID

REMS 指令:读取 1 字节制造商 ID 与 1 字节器件 ID

支持串行闪存可发现参数(SFDP)模式

硬件特性

串行时钟(SCLK)输入

串行时钟信号输入端

SI/SIO0

串行数据输入引脚;或在双 I/O 读取模式、四 I/O 读取模式下,作为串行数据输入 / 输出引脚

SO/SIO1

串行数据输出引脚;或在双 I/O 读取模式、四 I/O 读取模式下,作为串行数据输入 / 输出引脚

SIO2

四 I/O 读取模式下的串行数据输入 / 输出引脚

SIO3

四 I/O 读取模式下的串行数据输入 / 输出引脚

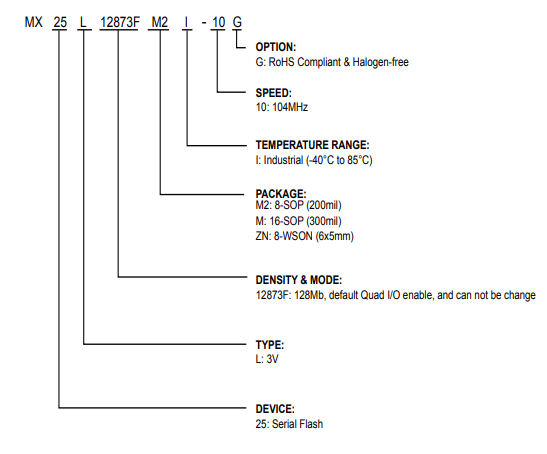

封装规格:

M2: 8-SOP (200mil)

M: 16-SOP (300mil)

ZN: 8-WSON (6x5mm)

全系列产品均符合有害物质限制指令要求,且为无卤产品

相关型号:MX25L12873FM2I-10G、MX25L12873FMI-10G

MX25L12873FZNI-10G Serial NOR Flash芯片概述:

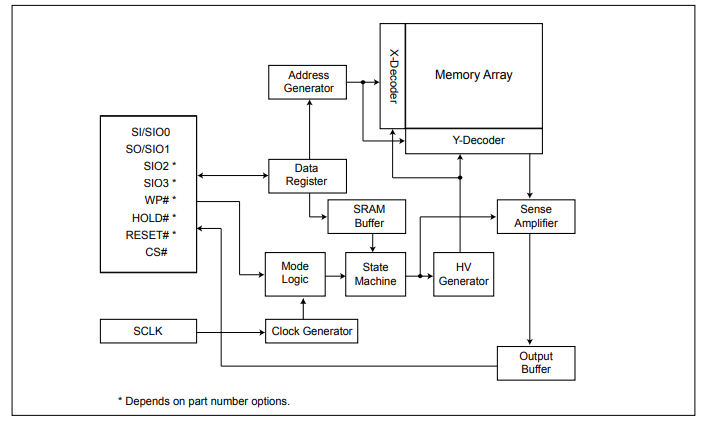

MX25L12873F是一款容量为 128Mb 的串行闪存,其内部默认配置为16,777,216×8 的存储架构。当工作于双 I/O 或四 I/O 模式时,存储架构将分别切换为 67,108,864×2 或 33,554,432×4。该器件集成串行外设接口与配套软件协议,在单I/O模式下可通过简易的三线总线实现数据传输,三条总线信号分别为:时钟输入(SCLK)、串行数据输入(SI)、串行数据输出(SO)。片选信号(CS#)输入有效时,器件将启动串行访问流程。

工作于双 I/O 读取模式时,原本的 SI 引脚与SO引脚将切换为SIO0引脚和 SIO1 引脚,用于传输地址 / 虚拟位输入信号与数据输出信号;工作于四I/O读取模式时,SI 引脚、SO 引脚则会扩展为 SIO0、SIO1、SIO2、SIO3 四根引脚,承担地址/虚拟位输入与数据输出功能。

MX25L12873F搭载旺宏专利的MXSMIO™(串行多I/O)技术,支持对整片闪存执行连续读取操作。

当器件接收到编程/擦除指令后,内置的自动编程/擦除算法将启动,完成对指定页、扇区或块地址的编程/擦除操作,并进行数据校验。编程操作支持按字节、按页(256 字节)或按字执行;擦除操作支持按扇区(4KB)、按块(32KB)、按块(64KB)或整片执行。

为简化用户接口设计,器件内置状态寄存器以实时反馈芯片工作状态。用户可发送状态读取指令,通过寄存器内的忙状态位(WIP) 判断编程或擦除操作的完成情况。

器件配备的高级安全特性可显著提升数据保护能力与安全等级,具体详情请参见 “安全特性” 章节。

当器件无操作且片选信号(CS#)为高电平时,将自动进入待机模式。

MX25L12873F采用旺宏独有的存储单元技术,即使经历 100,000 次编程 / 擦除循环,仍能保证存储数据的可靠性。

数据保护

在电源切换过程中,可能会出现异常的系统级信号,进而导致误擦除或误编程操作。本器件内置保护机制,可有效防止此类意外写入行为。

上电过程中,状态机将自动复位至待机模式。此外,器件的控制寄存器架构作出限制:只有在成功执行特定指令序列后,才能对存储器内的数据进行修改。

下文列出多项保护特性,可防止电源上电、掉电阶段或系统噪声引发的意外写入操作:

有效指令长度校验:对指令长度进行校验,确保指令以字节为单位,且在字节边界处完成传输。

写使能(WREN)指令:在执行任何修改数据的指令前,必须先发送写使能指令,将写使能锁存位(WEL)置位。

深度掉电模式:进入深度掉电模式后,除深度掉电解除指令(RDP)、读取电子签名指令(RES) 及软复位指令外,器件将拒绝执行其他所有写入类指令,以此实现保护。

高级安全特性:内置多重保护与安全机制,可防止数据被意外改写或恶意访问。