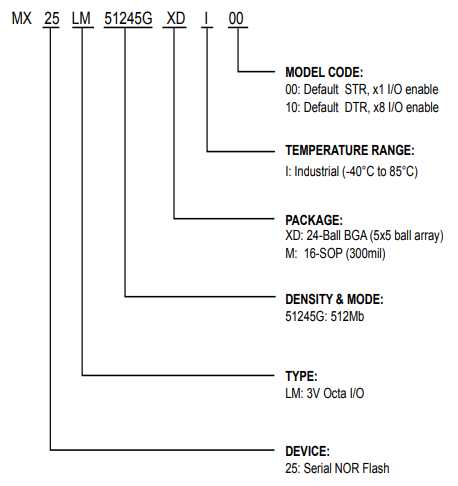

MX25LM51245G 3V 512M-BIT [x 1/x 8] CMOS octaflash Memory

MXIC(台湾旺宏电子)MX25LM51245GXDI00 Serial NOR Flash芯片特点:

通用

支持串行外围接口——模式0

单电源操作

-2.7至3.6伏用于读取、擦除和编程操作

512Mb:536870912 x 1位结构或67108864 x 8位(八位I/O模式)结构

协议支持

-单I/O和八I/O

-支持DTR(双倍传输速率)模式

快速频率支持

-支持时钟频率高达

-单输入/输出模式:133MHz

-Octa I/O模式:133MHz

-OPI读取操作的可配置虚拟循环数

提供Octa外围接口(OPI)

相等扇区,每个扇区4K字节,或相等块,每个块64K字节

-任何块都可以单独擦除编程:

-256字节页面缓冲区

-Octa输入/输出页面程序,以提高程序性能

典型的100000次擦除/编程周期

20年数据保留

软件功能

输入数据格式

-SPI:1字节命令代码

-OPI:2字节命令代码

高级安全功能

-闭锁保护

BP0-BP3和T/B状态位定义了要防止编程和擦除的区域大小指示

-高级扇区保护(固体和密码保护)

额外的8K位安全OTP

-具有唯一标识符

-工厂锁定可识别,客户可锁定

命令重置

编程/擦除暂停和恢复操作

电子身份识别

-JEDEC 1字节制造商ID和2字节设备ID

支持串行闪存可发现参数(SFDP)模式

硬件功能

SCLK输入

-串行时钟输入

SIO0-SIO7

-串行数据输入或串行数据输出

DQS

-数据选通信号

重置#

-硬件复位引脚

封装规格

16-pin SOP (300mil)

24-Ball BGA (5x5 ball array)

所有设备均符合RoHS和卤素标准-自由

MX25LM51245GXDI00 Serial NOR Flash芯片概述

MX25LM51245G是512Mb位八口串行NOR闪存,配置为67108864 x8内部。MX25LM51245G具有串行外围接口和软件协议,允许在简单的3线总线,而它处于单I/O模式。三个总线信号是时钟输入(SCLK)、串行数据输入(SI)和时钟输出(SCLC),以及串行数据输出(SO)。通过CS#输入启用对设备的串行访问。

MX25LM51245G八闪存在整个芯片上提供顺序读取操作。

发出编程/擦除命令后,自动编程/擦除算法,用于编程/擦除和验证将执行指定的页面或扇区/块位置。程序命令按字节或页(256)执行以字节为基础或以字为基础。擦除命令在扇区(4K字节)、块(64K字节)或整个芯片上执行基础。

为了给用户提供易于使用的界面,包括一个状态寄存器来指示芯片的状态。状态已读取可以发出命令,通过WIP位检测编程或擦除操作的完成状态。

当设备未运行且CS#为高时,它将进入待机模式。

MX25LM51245G采用Macronix专有的存储单元,即使在100000个编程和擦除周期。