Flash芯片技术解析

一、核心技术特性

Flash芯片作为非易失性存储器(NVM),采用电荷俘获效应实现数据持久化存储。其核心特征表现为:

断电数据保持:通过浮动栅极电荷锁定机制,确保数据在断电后长期稳定保存(典型保持周期达10年以上)

电可擦写特性:区别于传统ROM,支持多次在线编程操作

二、主流架构对比与演进

型 技术特征 典型应用场景 技术演进

NOR Flash • XIP架构(Execute-In-Place)

• 随机访问速度≤100ns

• 单元密度0.5-4Gb 嵌入式系统启动代码

工业控制固件存储 SPI接口提速至400MHz+

多I/O并行架构

NAND Flash • 顺序访问架构

• 页编程速度≤200μs

• 单元密度512Gb-1Tb 大容量存储介质

数据中心SSD 3D堆叠技术(当前主流232层)

QLC/PLC技术

技术演进里程碑:

2D→3D转型:平面微缩极限突破(<15nm时量子隧穿效应显著),3D堆叠使存储密度提升5-8倍

单元多值化:SLC→MLC→TLC→QLC→PLC,单Die容量从4Gb提升至1Tb,擦写寿命从10^5次降至10^3次

接口速率跃升:ONFI 5.0标准实现2400MT/s速率,PCIe 5.0 x4接口带宽达16GB/s

三、关键技术挑战与解决方案

耐久性管理:

磨损均衡算法:动态地址映射(Dynamic Wear Leveling)结合静态均衡(Static Wear Leveling)

坏块管理:出厂预标记+运行时坏块替换表(BBT)

读干扰抑制:读电压补偿算法(Read Retry)

数据完整性保障:

ECC纠错体系:LDPC纠错码支持4Kb/页纠错能力,纠错能力从SLC的1bit/512B提升至QLC的120bits/1KB

RAID架构:企业级SSD采用FTL层RAID 5/6数据冗余

性能优化技术:

并行通道架构:多Die/Plane并行操作(如8通道设计)

SLC缓存加速:TLC/QLC颗粒配置模拟SLC缓存区(Pseudo SLC)

四、新型存储技术对比

技术 原理 优势 产业化进程

3D XPoint 体电阻变化 字节寻址/μs级延迟 英特尔Optane产品线

MRAM 磁隧道结效应 无限次擦写/抗辐射 车载ECU领域应用

ReRAM 阻变效应 4F²单元尺寸/低操作电压 40nm工艺量产阶段

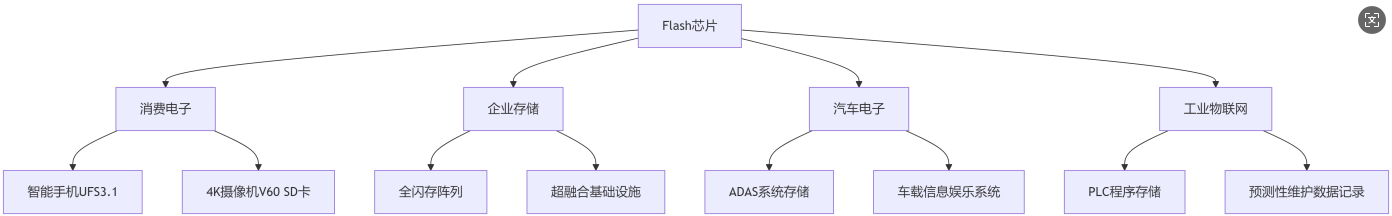

五、行业应用拓扑

六、前沿发展方向

存算一体架构:基于Flash的模拟存内计算(AiMC),能效比提升100倍

CXL互联生态:支持Compute Express Link协议的新型SSD架构

量子点技术:采用原子级精度制造工艺突破3D NAND堆叠层数限制

低温存储方案:-40℃环境下数据保持能力提升技术

前瞻性技术展望:涵盖存算一体等前沿方向