芯片工作原理图解

一、引言

芯片,学名集成电路(Integrated Circuit,简称 IC),是现代电子信息产业的核心基石,更是数字时代的 “大脑”。从智能手机、笔记本电脑到汽车电子、工业机器人,再到航天航空设备,几乎所有智能电子设备的运行,都依赖于芯片的精准控制与数据处理。

它的核心本质,是通过微米级乃至纳米级的精密加工工艺,将数亿甚至上百亿个晶体管、电阻器、电容器等无源元件,高密度集成在一块微小的单晶硅片上,实现电路功能的高度集成化、微型化与低功耗化。本文将结合结构拆解 + 信号流转 + 核心技术概念的图解逻辑,系统解析芯片的工作原理,帮助读者从宏观到微观理解其运行机制。

二、芯片的基本结构

芯片的内部结构如同一个精密的 “微型城市”,各功能模块协同配合,共同完成信号处理任务,以下为各核心结构的图解细节与拓展说明:

1. 硅片基底:芯片的 “生命土壤”

核心材料:芯片的基底采用单晶硅(Silicon),而非普通硅材料。单晶硅具有规整的晶体晶格结构,具备优异的半导体特性 —— 既非导体也非绝缘体,通过掺杂(掺入硼、磷等杂质)可精准调控其导电类型(P 型 / N 型),为晶体管的形成奠定基础。

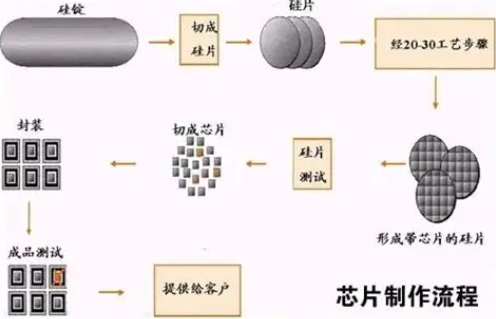

加工工艺:硅片需经过切割、抛光、清洗等预处理,形成直径从几英寸到 12 英寸不等的晶圆(Wafer),再通过光刻、蚀刻、掺杂等多轮工艺,在其表面逐层构建电路结构。

图解要点:可在图示中标注单晶硅的晶格结构,以及掺杂后形成的 P/N 结区域,直观展示半导体导电特性的原理基础。

2. 晶体管:芯片的 “功能细胞”

晶体管是芯片中最基础、最核心的元件,被称为芯片的 “开关”,其性能直接决定芯片的运算速度、功耗与集成度。

核心组成:以最经典的 **MOSFET(金属氧化物半导体场效应晶体管)为例,结构包含源极(Source)、漏极(Drain)、栅极(Gate)** 三个核心电极。

工作逻辑:通过在栅极施加电压,可改变栅极下方绝缘层的电场强度,进而控制源极与漏极之间的电流通断 —— 栅极电压达到阈值时,晶体管 “导通”,电流通过;未达阈值时,晶体管 “关断”,电流阻断。

拓展说明:目前主流芯片采用 **FinFET(鳍式场效应晶体管)或GAA(全环绕栅极晶体管)** 架构,通过增加晶体管 “有效宽度”、减小栅极漏电,实现 7nm、3nm 等先进工艺下的性能提升,图解时可标注两种架构的结构差异。

3. 互连线:芯片的 “交通网络”

芯片内部集成了数十亿个晶体管,若要实现复杂的逻辑运算,必须通过互连线将各元件高效连接,形成完整的电路网络。

材质与规格:互连线主要采用 ** 铜(Cu)** 材质(替代传统的铝),因其导电性更好、电迁移抗性更强;线宽从微米级逐步缩减至纳米级,最精细的互连线宽度已不足 10nm。

层级结构:芯片互连线分为 ** 金属层(Metal Layer)与通孔(Via)** 两部分 —— 金属层负责横向传输信号,通孔负责垂直连接不同金属层,多层堆叠构建复杂网络。

图解要点:可绘制多层金属层与通孔的立体结构示意图,标注不同层级线宽的差异,以及信号传输的路径方向。

4. 封装层:芯片的 “保护外壳与接口”

封装是芯片从晶圆走向应用的关键环节,兼具保护、散热、接口连接三大核心功能。

核心作用:① 物理保护:隔绝外界灰尘、湿气、机械冲击,保护内部脆弱的硅片;② 散热导出:将芯片工作时产生的热量传递至外部,防止过热损坏;③ 电气连接:通过引脚、焊球等结构,实现芯片内部与外部电路的信号、电源传输。

主流封装类型:根据应用场景不同,封装形式多样 ——**DIP(双列直插)** 适用于早期实验电路;**SOP/SOIC(小外形封装)** 体积小巧,广泛用于消费电子;**QFP(方型扁平封装)** 引脚众多,适配高性能 MCU;BGA(球栅阵列)、**QFN(无引线芯片封装)** 则是手机、服务器芯片的主流选择,图解时可对比不同封装的外观与引脚结构。

三、芯片的工作原理图解

芯片的运行本质是 **“信号输入→内部处理→信号输出”** 的闭环过程,以下为简化版图解流程的详细拆解,配合图示逻辑可更直观理解:

1. 输入信号:外部指令的 “入口”

信号类型:外部设备产生的电信号通过芯片的引脚(Pin)或焊球(Bump)进入芯片内部,主要分为两类:

数字信号:离散的 0/1 电平信号,是逻辑运算、数据处理的核心信号(如 CPU 的指令信号、存储芯片的读写信号);

模拟信号:连续变化的电压 / 电流信号(如麦克风采集的声音信号、传感器采集的温度信号),需经芯片内部的模数转换器(ADC)转换为数字信号后,才能被处理。

图解设计:在图示中用箭头标注输入信号的来源(如外部传感器、电源),以及信号进入芯片的引脚位置,区分数字 / 模拟输入引脚的不同标识。

2. 信号处理:内部逻辑的 “运算核心”

输入信号进入芯片后,会根据信号类型,传输至对应的功能模块进行处理,核心处理环节包括:

基础逻辑运算:由晶体管组成的门电路(与门、或门、非门、与非门等)构成基础运算单元,实现最基本的逻辑判断;多个门电路组合形成触发器、寄存器,再进一步组成算术逻辑单元(ALU),完成加减乘除、数据比较等复杂运算。

信号转换与调理:针对模拟输入信号,通过 ** 模数转换器(ADC)将其转化为数字信号;处理完成后,再通过数模转换器(DAC)** 将数字信号还原为模拟信号输出;同时还会进行信号放大、滤波、降噪等处理,提升信号质量。

时序同步与控制:芯片内部所有模块的协同运作,依赖时钟信号(Clock Signal)—— 由外部振荡器产生的周期性脉冲信号,如同 “指挥棒”,同步各模块的操作时序,确保信号处理的准确性与有序性。

功耗管理:现代芯片(尤其是移动设备芯片)集成了功耗管理模块,通过动态电压调整、时钟门控、睡眠模式等技术,在保证性能的同时降低功耗,延长设备续航。

图解要点:可绘制芯片内部功能模块框图(如 ALU、寄存器、ADC/DAC、时钟模块),用箭头标注信号在各模块的传输路径,以及时钟信号的同步控制逻辑。

3. 输出信号:处理结果的 “对外传递”

经过内部处理的信号,通过芯片的输出引脚传输至外部设备,或传递给其他芯片进行后续处理,具体应用场景包括:

控制外部设备的动作(如 MCU 控制电机转动、LED 灯亮灭);

输出处理后的数据(如存储芯片读取的数据、图像传感器处理后的图像信息);

反馈状态信号(如芯片的工作状态、故障提示信号)。

图解设计:标注输出信号的目标设备(如外部电机、显示屏、其他芯片),以及输出引脚与外部电路的连接方式,区分不同类型输出信号的传输方向。

四、关键概念图解拓展

为帮助读者更深入理解芯片工作原理,以下补充核心概念的图解解析与拓展知识:

1. 门电路:芯片逻辑的 “最小单元”

定义:门电路是由多个晶体管组成的、实现基本逻辑运算的电路,是构成所有复杂数字电路的基础。

核心类型与功能:

与门:所有输入信号为高电平时,输出才为高电平(实现 “逻辑与”);

或门:任意一个输入信号为高电平时,输出即为高电平(实现 “逻辑或”);

非门:输入与输出电平相反(实现 “逻辑非”,也叫反相器);

与非门、或非门:分别是与门 + 非门、或门 + 非门的组合,是实际应用中最常用的门电路。

图解与拓展:绘制每种门电路的晶体管电路图、真值表(输入与输出的对应关系),以及逻辑符号,同时说明门电路的开关速度、扇出能力等性能指标,以及其对芯片运算效率的影响。

2. 时钟信号:芯片运作的 “时间标尺”

特性:时钟信号是周期性的方波信号,具有固定的频率(单位:Hz),频率越高,芯片单位时间内能完成的运算次数越多,性能越强。

同步机制:芯片内部的寄存器、ALU 等模块,均在时钟信号的上升沿 / 下降沿完成数据的读取与存储,实现无差错的时序协同。

拓展说明:主频是芯片时钟频率的直观体现(如 3GHz 的 CPU,意味着时钟每秒振荡 30 亿次),但频率并非越高越好,还需考虑功耗、散热与制程工艺限制,图解时可标注时钟频率与芯片性能、功耗的关系曲线。

3. 功耗管理:芯片续航的 “核心策略”

核心技术:

动态电压调整(DVFS):根据芯片负载情况,动态调整工作电压和频率 —— 高负载时提高电压 / 频率,保证性能;低负载时降低电压 / 频率,减少功耗。

时钟门控:关闭闲置模块的时钟信号,阻止其进行无效运算,从根源上降低功耗。

睡眠 / 深度睡眠模式:芯片闲置时切换至低功耗模式,关闭部分非核心模块的供电,仅保留基础控制功能。

图解要点:绘制功耗管理模块与各功能模块的连接示意图,标注不同模式下芯片的功耗变化曲线,以及触发模式切换的条件(如负载率、设备电量)。

4. 封装与性能的关联

不同封装类型直接影响芯片的散热能力、引脚数量与应用适配性,进而影响其工作效率:

BGA 封装:引脚数量多、密度大,散热效果好,适合高性能服务器芯片、手机 SoC,但封装成本较高,需配合专用的 PCB 板焊接;

QFN 封装:无引脚设计,体积小巧,散热效率较高,适用于消费电子类芯片(如 MCU、电源管理芯片);

DIP 封装:引脚可直接插入电路板,安装拆卸方便,适合实验与维修,但体积大、引脚数量少,仅适用于低性能、低集成度芯片。

图解对比:绘制主流封装类型的实物图、结构剖面图,标注各自的散热路径、引脚布局,以及适用的芯片场景。

五、总结

芯片的工作过程,是硅基底为载体、晶体管为核心、互连线为网络、封装为接口的多模块协同过程,通过 “信号输入 - 内部逻辑处理 - 信号输出” 的闭环,实现对电子设备的控制与数据处理。

从微观的晶体管开关,到宏观的系统级运算,芯片的每一个环节都凝聚着精密的工艺与技术智慧。后续制作图解时,可结合上述拓展内容,补充结构示意图、信号流转图、参数对比表等视觉元素,既能让读者直观理解原理,也能体现专业深度。