DRAM(动态随机存取存储器)作为当代电子设备核心存储器件,凭借读写速度快、数据实时存取的优势,广泛应用于计算机、服务器、智能手机、人工智能终端等领域,其核心存储单元为经典的1T1C结构(1个晶体管+1个存储电容),是实现高密度、大容量数据存储的基础。DRAM芯片制造属于超精密半导体工艺范畴,整条产线融合光刻、蚀刻、离子注入、薄膜沉积、化学机械抛光(CMP)、3D堆叠等数十道核心工序,工艺精度达到纳米甚至亚纳米级别,对设备精度、材料纯度、工艺控制要求极高,最终实现存储密度、读写带宽、能效比的持续升级。下文将从核心制造流程、先进技术迭代、行业核心挑战三大维度,全面拆解DRAM芯片制造体系。

一、DRAM芯片核心制造全流程

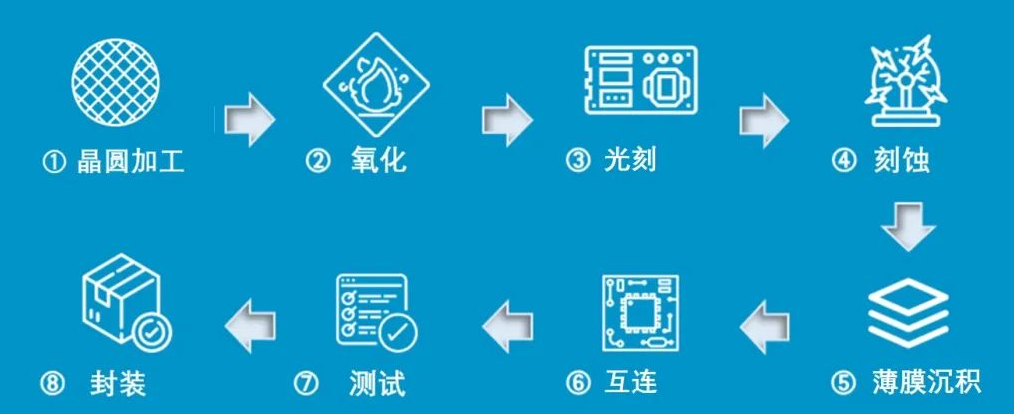

DRAM制造整体分为前道晶圆制程(FEOL)、存储单元核心制备、后道互连制程(BEOL)、封装测试四大核心阶段,每一个阶段环环相扣,直接决定芯片的良品率、性能与存储容量。

(一)晶圆准备与前道工艺(FEOL):奠定芯片基础架构

前道工艺是DRAM制造的根基,核心目标是在高纯度单晶硅晶圆上完成晶体管基底、存储单元阵列及外围电路的初步成型,为后续电容与互连工艺搭建框架。

制造起始于高纯度单晶硅晶圆生长,选用纯度高达99.9999999%(11个9)的电子级多晶硅,通过直拉法(CZ)或区熔法(FZ)生长成单晶硅棒,再经切割、研磨、抛光,形成表面极致平坦、无缺陷的抛光晶圆。晶圆上线后,首先经过多轮化学清洗与物理抛光,彻底去除表面颗粒、有机污染物与氧化层,保障后续工艺的精度;随后通过热氧化工艺在晶圆表面形成一层均匀的二氧化硅绝缘层,隔绝后续器件的电流串扰。

接下来进入核心光刻环节,通过光刻胶涂布、曝光、显影,精准定义存储单元阵列区(Active Area,AA)与外围控制电路区域,这是决定DRAM存储密度的关键步骤。随着半导体技术节点持续微缩,AA区域的半间距不断缩小,传统光刻技术无法满足纳米级图案成型需求,因此先进制程普遍采用多重曝光技术,包括LELE(光刻-蚀刻-光刻-蚀刻)、SADP(自对准双重图案化)、SAQP(自对准四重图案化),而10nm以下先进节点则全面引入EUV(极紫外)光刻技术,实现亚10nm级精密图案成型,最大限度缩小存储单元占用面积。

光刻完成后,通过离子注入工艺实现晶圆区域选择性掺杂:在存储阵列区精准注入杂质离子,形成P型阱区(Pwell)与N型源/漏极,构建1T1C单元的晶体管通道;在外围电路区则分别完成NMOS与PMOS晶体管的掺杂结构制备,形成控制存储单元读写的逻辑电路。随后采用埋入式字线(BWL)技术,在晶圆表面刻蚀深沟槽,依次沉积氮化钛(TiN)与钨(W)形成栅极结构,将字线埋入晶圆内部,相比传统字线结构,大幅降低接触电阻,提升晶体管开关速度与响应性能,同时优化存储单元空间布局,进一步提升密度。

(二)存储电容制造:1T1C单元的核心储能部件

存储电容是DRAM实现数据存储的核心,依靠电容内电荷存储判断数据0/1状态,其容量、漏电流特性直接决定DRAM的数据保持时间与稳定性。受限于存储单元面积微缩,现代DRAM电容普遍采用堆叠式或深沟槽式两种高集成度结构,通过极致的高纵横比(HAR)微孔设计,在极小空间内最大化电极接触面积,弥补单元面积缩小带来的电容值衰减问题。

工艺层面,首先通过高深宽比蚀刻工艺制备电容存储节点(SN)微孔,孔径达到纳米级别,孔深与孔径比值远超传统半导体结构;随后在微孔内壁沉积高k介电材料,替代传统二氧化硅介电层,主流先进介电材料包括镧掺杂氧化铪(La:HfO₂)、氧化锆/氧化铝/氧化锆叠层结构,这类材料介电常数远高于传统材料,既能保证绝缘性能,又能大幅提升单位面积电容值。电容顶电极选用导电性与稳定性优异的氮化钛(TiN),内部填充硅锗(SiGe)等导电材料,进一步扩大电极有效面积,同时降低漏电流,延长数据刷新周期。

此外,3D堆叠技术逐步融入电容制备环节,通过硅通孔(TSV)或晶圆键合技术,实现多层存储单元垂直集成,突破平面布局的密度瓶颈,同步提升芯片存储容量与数据传输带宽,适配高端服务器、HBM(高带宽内存)等高端应用场景。

(三)后道工艺(BEOL):实现芯片电路互连导通

前道工艺完成存储单元与晶体管制备后,后道工艺核心目标是实现各器件之间的电路互连,构建完整的信号传输通路,保障数据读写、传输、控制指令的顺畅执行。

该阶段首先完成关键接触孔制备,包括位线接触(BLC)、存储节点接触(SNC),分别打通晶体管与位线、存储电容与位线的电气连接,这一步的工艺精度直接影响数据读取的灵敏度与稳定性。随后进行第一层金属互连(M1)制备,通过光刻、蚀刻、金属沉积、CMP工艺,形成精细化金属导线;随着制程升级,DRAM内部互连层数持续增加,多层互连结构需通过反复CMP工艺保障表面平坦度,配合自对准互连技术,精准控制层间对准误差(Overlay),避免线路偏移导致的信号干扰或短路问题。同时,外围电路MOSFET的栅极优化、源漏极扩展工艺也在此阶段同步完成,进一步提升外围控制电路的响应速度与驱动能力。

(四)封装与测试:成品化与性能验证

晶圆级工艺全部完成后,进入封装测试阶段,将整片晶圆转化为可直接应用的DRAM成品,同时筛选出合格芯片,保障终端产品可靠性。

首先通过精密晶圆切割工艺,将整片晶圆分割为单颗DRAM裸片(Die),切割过程需严格控制应力,避免损伤内部存储单元;随后进行封装键合,主流封装方式包括传统金线键合与先进倒装芯片(Flip Chip)工艺,倒装芯片凭借更小的封装体积、更低的传输延迟,成为先进DRAM封装的主流选择。裸片通过键合工艺固定在封装基板上,形成内存条(DIMM)、嵌入式DRAM等不同封装形态,满足消费电子、服务器、车载等不同场景需求。

封装完成后,进入严苛的测试环节,包括芯片功能测试、读写性能测试、高低温老化测试、电气性能验证、稳定性测试等多项流程,全面检测芯片的存储容量、读写速度、数据保持能力、功耗指标,确保每一颗成品芯片完全符合行业规格与客户需求,剔除性能不达标、存在缺陷的次品,保障最终产品的良率与可靠性。

二、DRAM先进制程迭代

随着大数据、人工智能、云计算等领域对存储容量与速度的需求持续攀升,DRAM制程持续微缩,核心技术不断迭代,核心发展方向聚焦于提升存储密度、降低功耗、扩大带宽、优化能效比四大维度,主流先进技术趋势如下:

- 存储单元布局持续优化:DRAM存储单元面积从早期8F²逐步缩减至6F²,再到当前先进节点的4F²紧凑型布局,配合垂直通道晶体管(VCT)与埋入式字线(BWL)技术,最大限度利用平面与垂直空间,实现单位面积存储密度翻倍提升,适配大容量内存产品需求。

- 高k金属栅极(HKMG)全面普及:替代传统多晶硅栅极结构,有效降低晶体管漏电流,减少静态功耗,同时提升晶体管开关速度与工作稳定性,缓解制程微缩带来的漏电失控问题,延长DRAM数据刷新间隔,降低整体运行功耗。

- EUV光刻与SAQP技术下沉:10nm以下先进DRAM节点,传统多重曝光技术难以满足图案精度与良率要求,EUV极紫外光刻配合SAQP自对准四重图案化技术,实现超精密图案成型,解决纳米级制程的工艺瓶颈,推动制程持续向亚10nm、7nm以下突破。

- 3D堆叠与HBM高带宽集成:突破平面存储密度上限,通过TSV硅通孔技术实现多颗DRAM芯片垂直堆叠,形成多层存储架构,数据带宽可达TB级别,完美适配AI算力、高端服务器、显卡等高带宽需求场景,成为下一代高端DRAM的核心发展方向。

- 异构集成与封装优化:采用先进异构封装技术,将DRAM与逻辑芯片、控制芯片整合封装,缩短信号传输路径,降低延迟与功耗,同时优化封装结构,实现更小体积、更高集成度,适配智能手机、车载电子等紧凑型终端设备。

三、DRAM芯片制造核心

DRAM制程持续微缩与3D集成技术推进的同时,制造环节面临的技术难题与成本压力也日益凸显,核心挑战集中在工艺精度、材料、良率、成本四大层面:

- 高精密器件微缩难度极大:存储电容与灵敏放大器作为DRAM核心器件,制程微缩后,高纵横比电容微孔的蚀刻均匀性、深孔内部薄膜沉积一致性极难控制,稍有偏差就会导致电容值不达标、漏电流过大;灵敏放大器尺寸缩小后,信号放大灵敏度下降,极易出现数据读取误差,对工艺控制精度提出极致要求。

- 光刻与对准精度瓶颈:先进节点下,光刻图案的线宽粗糙度、层间Overlay对准误差直接决定芯片良率,哪怕是纳米级的误差,都会导致存储单元短路、断路,EUV光刻设备成本高昂、工艺调试复杂,进一步加大量产难度。

- 3D堆叠与封装复杂性飙升:多层芯片垂直堆叠后,TSV硅通孔的布线密度、键合精度、热应力匹配问题凸显,多层堆叠容易出现芯片变形、信号串扰,封装工艺复杂度与生产成本大幅提升,良率控制难度远超平面DRAM。

- 亚10nm节点量子效应干扰:10nm以下先进制程中,半导体器件尺寸逼近原子级别,量子隧穿效应导致晶体管漏电流急剧增加,信号干扰问题加剧,传统器件结构失效,需要全新的材料体系与器件结构设计,研发与量产门槛极高。

四、总结

DRAM芯片制造是一条高度复杂、精密且技术密集型的完整工艺链,涵盖晶圆预处理、前道器件制备、核心电容成型、后道互连、先进封装、全流程测试六大核心模块,每一道工序都凝聚了当代半导体顶尖技术成果。以1T1C存储单元为核心,依托制程微缩、高k材料、EUV光刻、3D堆叠等核心技术,DRAM产品持续实现密度、带宽、能效的迭代升级,支撑全球数字经济与高端电子产业发展。

尽管当前面临工艺微缩、量子效应、成本控制等多重挑战,但随着材料创新、工艺优化与封装技术的持续突破,DRAM制造工艺将不断突破瓶颈,朝着更高密度、更低功耗、更大带宽、更高集成度的方向发展,持续适配人工智能、云计算、车载智能、边缘计算等新兴领域的存储需求,成为数字时代核心存储硬件的核心支撑。找DRAM芯片代理商就找深圳市微效电子有限公司,代理晶豪科技DRAM芯片系列产品;