XM25QH128C

XM25QH128CHIQU08Q芯片型号介绍:

3V 128M-BIT

SERIAL FLASH MEMORY WITH

DUAL/QUAD SPI & QPI

特征

SpiFlash记忆新家族

–XM25QH128C:128M位/16M字节

–标准SPI:CLK、/CS、DI、DO、/WP、/Hold

–双SPI:CLK、/CS、IO0、IO1、/WP、/Hold

–四路SPI:CLK、/CS、IO0、IO1、IO2、IO3

–QPI:CLK、/CS、IO0、IO1、IO2、IO3

最高性能串行闪存

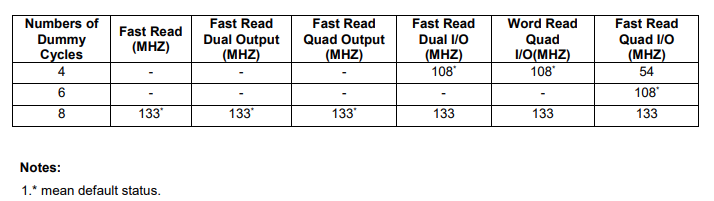

–133MHz单、双/四SPI时钟

–可配置的虚拟循环数,用于快速读取

行动

–超过100000个擦除/编程周期

–超过20年的数据保留

–带8/16/32/64字节环绕的突发读取

高效的“连续读取”和QPI模式

–使用8/16/32/64 ByteWrap进行连续读取

–四外设接口(QPI)减少

指令开销

–允许真正的XIP(就地执行)操作

高性能编程/擦除速度

–页面编程时间:典型值为0.5ms

–扇区擦除时间:典型值为40ms

–32KB块擦除时间通常为120ms

–64KB块擦除时间通常为250ms

芯片擦除时间:典型值为55秒

宽功率范围,宽温度范围

–全电压范围:2.3-3.6V

–18mA最大有效读取电流

– 5最大超深断电电流

–-40°C至+105°C工作范围

4KB扇区的灵活架构

–均匀扇区/块擦除(4K/32K/64K字节)

–每个可编程页面编程1到256字节

–擦除/程序暂停和恢复

高级安全功能

–软件和硬件写保护

–电源锁定和OTP保护

–顶部/底部,补充阵列保护

–每个设备的64位唯一ID

–支持串行闪存可发现参数

(SFDP)签名

–3套可锁定的256字节OTP安全页面

–易失性和非易失性状态寄存器位

空间高效包装

–标准操作规程/VSOP 2.08亿8L

–WSON 5x6 8L

–WLCSP 21球

–联系XMC获取KGD和其他选项

一般说明

XM25QH128C(128M位)串行闪存为空间有限的系统提供了一种存储解决方案,

引脚和电源。25Q系列提供了远远超出普通串行闪存设备的灵活性和性能。

它们非常适合用于将代码阴影转移到RAM、直接从双/四SPI(XIP)执行代码以及存储语音,

文本和数据。该设备在单个2.3V至3.6V电源上运行,电流消耗低至

1µA用于超深度断电。所有设备都提供节省空间的包装。

XM25QH128C阵列被组织成65536个可编程页面,每个页面256字节。最多256字节

可以一次编程。页面可以按16组(4KB扇区擦除)、128组(32KB扇区擦除)进行擦除

块擦除)、256组(64KB块擦除)或整个芯片(芯片擦除)。XM25QH128C有4096个

可擦除扇区和256个可擦除块。4KB的小扇区提供了更大的灵活性

需要数据和参数存储的应用程序。(见图2。)

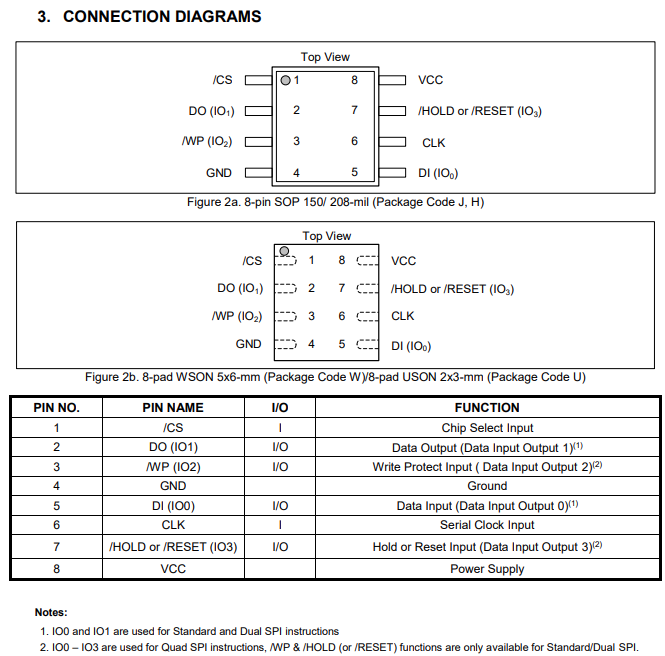

XM25QH128C支持标准串行外围接口(SPI)、双/四路I/O SPI以及2块

指令周期四外设接口(QPI):串行时钟、芯片选择、串行数据I/O 0(DI)、I/O 1(DO)、,

I/O2(/WP)和I/O3(/HOLD)。支持高达133MHz的SPI时钟频率,允许等效时钟

使用快速读取双/四输入/输出和QPI时,双输入/输出的速率为266MHz,四输入/输入的速率为532Mhz

说明。这些传输速率可以优于标准异步8位和16位并行闪存。

连续读取模式允许高效的内存访问,指令开销低至8个时钟

读取24位地址,允许真正的XIP(就地执行)操作。

保持引脚、写保护引脚和可编程写保护,带顶部或底部阵列控制,提供

进一步的控制灵活性。此外,该设备支持JEDEC标准制造商和设备ID

SFDP寄存器、一个64位唯一序列号和三个256字节的安全寄存器。

4.信号描述

4.1芯片选择(/CS)

SPI芯片选择(/CS)引脚启用和禁用设备操作。当/CS为高时,设备为

取消选择,串行数据输出(DO或IO0、IO1、IO2、IO3)引脚处于高阻抗。什么时候

如果取消选择,设备功耗将处于待机状态,除非进行内部擦除、编程

或者写入状态寄存器循环正在进行中。当/CS变低时,将选择设备,电源

消耗将增加到活动水平,指令可以写入和读取

设备。通电后,/CS必须从高转换到低,然后才能接受新的指令。

/CS输入必须在加电和断电时跟踪VCC电源电平(请参阅“写保护”和

图45)。如果需要,可以使用/CS引脚上的上拉电阻器来实现这一点。

4.2串行数据输入、输出和IO(DI、DO和IO0、IO1、IO2、IO3)

XM25QH128C支持标准SPI、双SPI和四SPI操作。标准SPI

指令使用单向DI(输入)引脚将指令、地址或数据串行写入

设备位于串行时钟(CLK)输入引脚的上升沿。标准SPI也使用单向

DO(输出)从CLK下降沿的设备读取数据或状态。

双SPI和四SPI指令使用双向IO引脚串行写入指令、地址或

将数据传输到CLK上升沿的设备,并在下降沿从设备读取数据或状态

CLK。四SPI指令要求状态寄存器2中的非易失性四启用位(QE)为

集。当QE=1时,/WP引脚变为IO2,/HOLD引脚变为IO 3。

4.3写保护(/WP)

写保护(/WP)引脚可用于防止状态寄存器被写入。用于

结合状态寄存器的块保护(CMP、SEC、TB、BP2、BP1和BP0)位,以及

状态寄存器保护(SRP)位,小至4KB扇区或整个内存阵列都可以

受到硬件保护。/WP引脚处于低电平活动状态。当状态寄存器-2的QE位设置为Quad时

I/O,/WP引脚功能不可用,因为该引脚用于IO2。引脚见图1a-c

配置四I/O操作。

4.4保持(/保持)

/HOLD引脚允许在设备处于活动选择状态时暂停设备。当/HOLD变低时,

当/CS为低时,DO引脚将处于高阻抗状态,DI和CLK引脚上的信号将为

忽略(不在乎)。当/HOLD变高时,设备操作可以恢复。/HOLD功能

当多个设备共享相同的SPI信号时,它可能很有用。/HOLD引脚处于低电平激活状态。

当状态寄存器-2的QE位设置为四输入/输出时,/HOLD引脚功能不可用,因为

该引脚用于IO3。四路I/O操作的引脚配置见图1a-c。

4.5串行时钟(CLK)

SPI串行时钟输入(CLK)引脚为串行输入和输出操作提供时序。(“参见

SPI操作”)

4.6重置(/Reset)

/RESET引脚允许控制器重置设备。对于8引脚封装,当QE=0时

IO3引脚可以配置为/HOLD引脚或/RESET引脚,具体取决于状态寄存器

设置。当QE=1时,/HOLD或/RESET功能不适用于8针配置