FT24C64A-ESR-T芯片型号:

双线串行EEPROM64K(8位宽)

FT24C64A-ESR-T特征

低电压和低功率操作:

FT24C64A:VCC=1.7V至5.5V

32 字节页写入模式。

允许部分页面写入操作。

内部组织:8192×8(64K)。

标准2线双向串行接口。

施密特触发器,用于噪声保护的滤波输入。

自定时写入周期(最大5ms)。

1000 kHz(2.5-5.5V)、400kHz(1.7V)兼容性。

写入操作前自动擦除。

写保护引脚用于硬件数据保护。

高可靠性:通常可承受1000000次循环。

100 年数据保留。

工业温度范围(-40℃至85℃)。

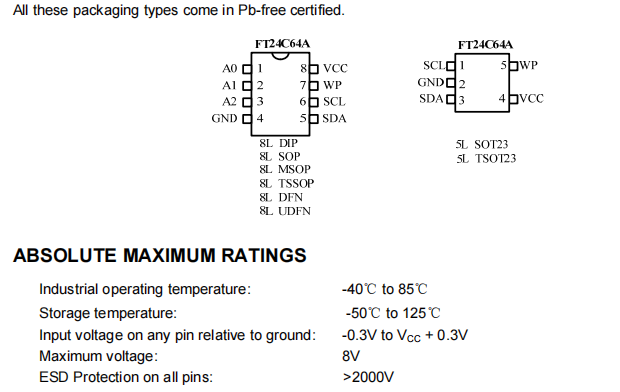

标准8引脚DIP/SOP/MSOP/TSSOP/DFN/UDFN和5引脚SOT23/TSOT23无铅封装。

FT24C64A-ESR-T说明

FT24C64A系列是65536位串行电可擦除可编程只读存储器,通常称为EEPROM。它们被组织为8192个字,每个字8位(一个字节)。设备采用专有的先进CMOS工艺制造,适用于低功耗和低电压应用。

这些器件有标准8导联DIP、8导联SOP、8导联MSOP、8导联TSSOP、8导联DFN、8引脚UDFN、5引脚SOT23和5引脚TSOT23封装。标准的2线串行接口是用于处理所有读写功能。我们的扩展VCC范围(1.7V至5.5V)器件可实现宽应用范围。

引脚说明

(A) 设备/芯片选择地址(A2、A1、A0)

这些是串行EEPROM设备的芯片选择输入信号。通常,这些信号是硬连线到VIH或VIL。如果未连接,它们在内部被识别为VIL。

(B) 串行时钟

SCL输入的上升沿是将数据锁存到EEPROM设备中,而SCL输入的下降沿是时钟是将数据从EEPROM设备中时钟输出。

(C) 串行数据线

SDA数据线是串行设备的双向信号。这是一个开漏输出信号,可以有线OR与其他开漏输出设备。

(D) 写保护(WP)

FT24C64A器件有一个WP引脚,用于保护整个EEPROM阵列免受编程。

如果WP引脚未连接或输入到VIL,则允许进行编程操作。相反,所有如果WP引脚连接到VIH或VCC,则编程功能被禁用。读取操作不受影响WP引脚的输入电平。

存储器结构

FT24C64A设备分别有256页。由于每页有32个字节,因此随机字对FT24C64A的寻址将分别需要13位数据字地址。

设备操作

(A) 串行时钟和数据转换

SDA引脚通常被外部电阻器拉到高电平。仅当满足以下条件时,才允许更改数据串行时钟SCL处于VIL。任何SDA信号转换都可能被解释为启动或停止状态

如下所述。

(B) 启动条件

当SCL≥VIH时,SDA从高到低的转变被解释为启动条件。全部有效命令必须以START条件开头。

(C) 停止条件

当SCL≥VIH时,SDA从低到高的转变被解释为STOP状态。所有有效阅读或写命令以STOP条件结束。如果超过以下时间,设备将进入待机模式读取命令。页面或字节写入命令后的STOP条件将触发芯片进入自定时内部编程完成后的待机模式(见图1)。

(D) 承认

2线协议以8位字的形式向EEPROM传输地址和数据。EEPROM在接收到每个单词后,通过输出“0”来确认数据或地址。承认信号出现在每个字之后的第9个串行时钟上。

(E) 待机模式

EEPROM在接收到STOP位后,在重新通电后进入低功耗待机模式在读取模式下或在完成自时内部编程操作后