芯片制造全流程解析:从硅砂到集成电路的精密之旅

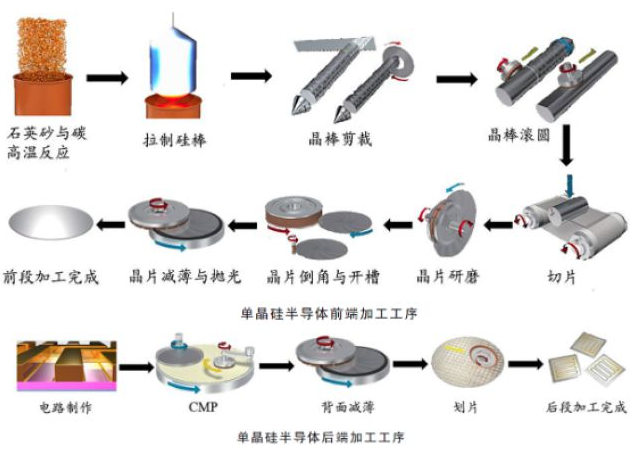

一、晶圆制备——芯片制造的"地基工程"

硅锭铸造

原料提纯:石英砂经高温碳还原得98%冶金级硅,经氯化蒸馏获得9N级高纯多晶硅

单晶生长:采用CZ法(主流)或FZ法,通过籽晶引导生长完美单晶硅棒,直径决定晶圆尺寸(主流300mm)

晶圆加工

精密切割:金刚石线锯将硅棒切割为0.7-0.8mm薄片

纳米级抛光:三步工艺实现原子级平整度(Ra<0.5nm)

外延增强:通过CVD法生长同质/异质外延层(如SiGe/Si)

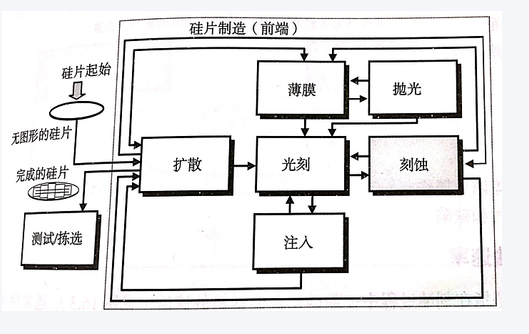

二、前道工艺核心制程

表面预处理

超净清洗:采用RCA标准流程(SC1/SC2/DHF)配合兆声波清洗,颗粒控制<10nm

热氧化:干法(O2)生长超薄栅氧(<2nm),湿法(H2O)生成厚场氧

图形化工程

(1) 光刻三部曲

旋涂:光刻胶厚度控制±1%(193nm ArF胶)

曝光:EUV光刻实现7nm节点,套刻精度<2nm

显影:碱性溶液选择性去除曝光区

(2) 刻蚀技术

干法刻蚀:ICP/RIE实现各向异性刻蚀,深宽比>40:1

湿法刻蚀:HF系溶液用于SiO2选择性去除

器件构建

离子注入:能量范围1keV-3MeV,剂量控制±1%

快速退火:毫秒级激光退火激活掺杂,抑制扩散

原子层沉积:ALD生长高k介质(HfO2, k≈25)

三、互连系统构建

铜互连革命

双大马士革工艺:先刻蚀介质沟槽,后电镀填铜

阻挡层创新:TaN/Ta复合层(厚度<2nm)防止铜扩散

化学机械抛光:终点检测精度±5nm,碟形凹陷<10nm

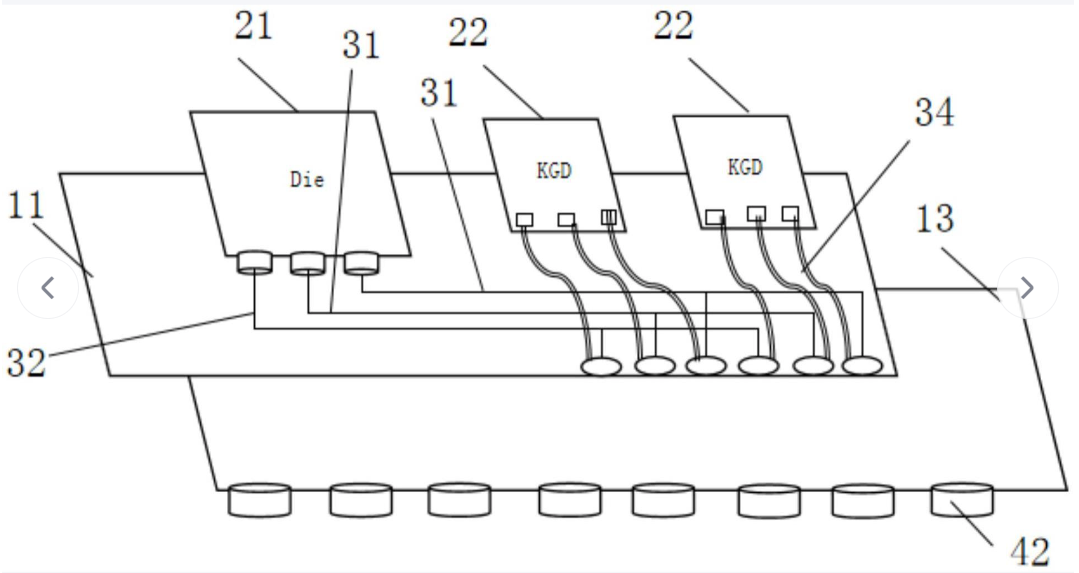

多层堆叠技术

低k介质:掺氟SiO2(k=3.6)到气隙结构(k<2.2)

TSV三维集成:深硅刻蚀(AR>10:1)+铜填充

四、工艺监控体系

在线检测

光学量测:椭偏仪膜厚测量精度±0.1nm

电子束检测:分辨率达0.5nm缺陷识别

晶圆验收测试

过程控制模块:包含500+测试结构

参数测试:栅极漏电流<1pA/μm,接触电阻<1Ω·μm²

五、技术演进趋势

材料革新:SiC/GaN宽禁带半导体应用

制造革命:GAA晶体管与3D NAND堆叠

设备突破:High-NA EUV光刻机数值孔径0.55

此流程凝聚了现代工业文明的最高制造精度,每个300mm晶圆需经历1000+工艺步骤,涉及300余种专用设备,最终实现百亿晶体管集成。芯片制造不仅需要超净环境(Class 1洁净度),更依赖材料科学、量子物理、精密机械等多学科协同创新,堪称人类工程智慧的巅峰之作。