IC封装(集成电路封装)是指将半导体芯片(Die)进行封装保护,并提供与外部电路进行电气连接和机械固定的外壳结构。封装技术直接影响芯片的性能、可靠性、功耗、散热、尺寸和成本。随着技术的发展,封装类型繁多,且不断创新。

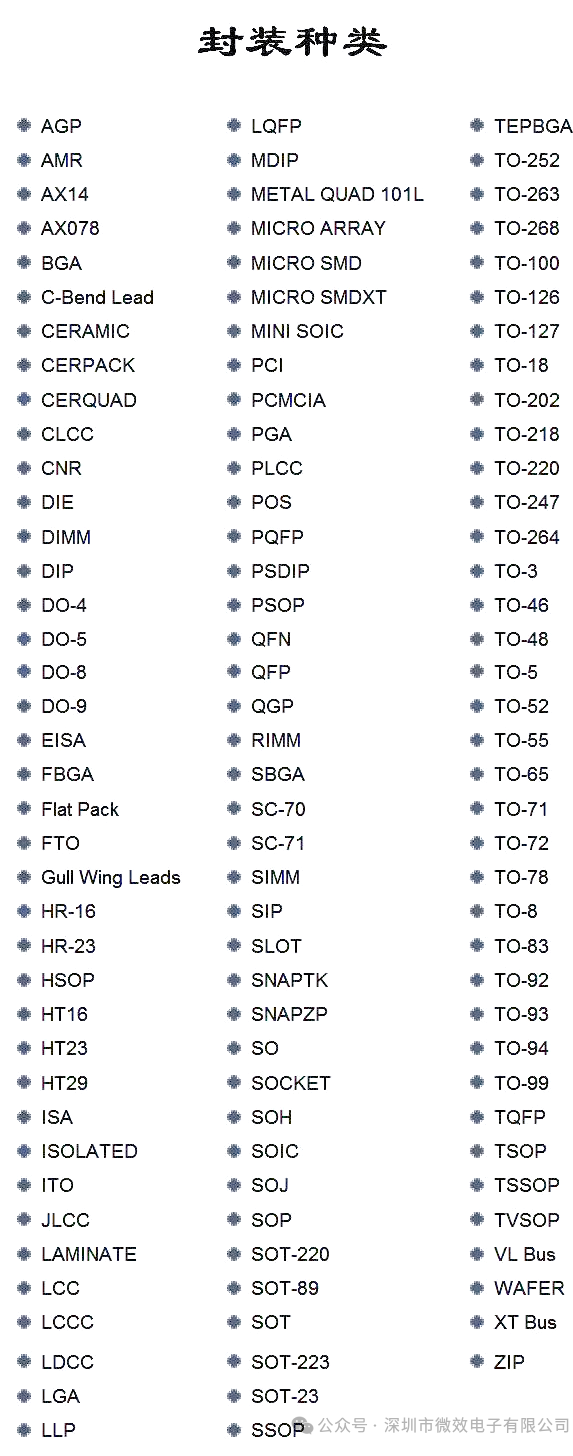

以下是一些主要的IC封装类型及其特点:

一、传统插装封装(Through-Hole Technology - THT)

特点: 引脚插入印刷电路板(PCB)上预先钻好的孔中,通常采用波峰焊进行焊接。机械强度高,但占用PCB面积大,密度低。

主要类型:

变种:SIP (Single In-line Package) - 单列直插封装。

变种:ZIP (Zigzag In-line Package) - 锯齿形单列直插封装。

DIP (Dual In-line Package): 双列直插式封装。两侧引脚平行向下延伸。是早期最经典的封装形式,常用于微处理器、存储器、逻辑IC等。引脚数通常较少(最多64脚左右)。

二、表面贴装封装(Surface Mount Technology - SMT)

特点: 引脚或焊端位于封装体侧面或底部,直接贴装在PCB表面的焊盘上,采用回流焊工艺。极大地提高了PCB组装密度和自动化程度,是目前绝对的主流。

主要类型:

变种:

LQFP (Low-profile QFP): 薄型QFP,高度更低。

TQFP (Thin QFP): 更薄的QFP。

FQFP/BQFP (Fine-pitch QFP / Bumpered QFP): 引脚间距更小(≤0.5mm),BQFP在四角有缓冲凸起防止引脚变形。

变种:

SSOP (Shrink SOP): 缩小型SOP,引脚间距更小(如0.65mm, 0.635mm)。

TSOP (Thin SOP): 薄型SOP,厚度显著减小,常见于存储器(尤其是DRAM、Flash)。

TSSOP (Thin Shrink SOP): 薄缩小型SOP,结合了SSOP的间距和TSOP的薄度。

SOP/SOIC (Small Outline Package / Small Outline Integrated Circuit): 小外形封装。两侧有翼形引脚(Gull Wing Lead)向外伸展。引脚间距通常为1.27mm或更小(如0.65mm)。应用非常广泛。

QFP (Quad Flat Package): 四侧引脚扁平封装。四边都有翼形引脚向外伸展。引脚间距较小(常见1.0mm, 0.8mm, 0.65mm, 0.5mm, 0.4mm)。适用于引脚数量较多的芯片(如微控制器、DSP、ASIC)。

QFN/DFN (Quad Flat No-leads / Dual Flat No-leads): 四边/双边无引脚扁平封装。封装体底部中央有一个大面积裸露的散热焊盘(Exposed Pad),四周是用于电气连接和焊接的表面贴装焊端(无向外延伸的引脚)。体积小、重量轻、热性能优异(散热焊盘直接焊接在PCB散热层上)、电气性能好(电感小)。应用极其广泛,从低功耗器件到射频、电源管理芯片。

PLCC (Plastic Leaded Chip Carrier): 塑料有引脚芯片载体。四边有J形引脚向内弯曲。通常需要插座使用(常用于可编程逻辑器件),也可直接焊接。

SOJ (Small Outline J-lead): 小外形J引脚封装。两侧有J形引脚。曾常用于DRAM模块。

LCCC (Leadless Ceramic Chip Carrier): 无引脚陶瓷芯片载体。陶瓷封装,四侧有镀金或焊料电极。可靠性高,成本高,用于军工、航天等高端领域。

三、高密度/阵列封装(High Density / Array Packaging)

特点: 引脚/焊球分布在封装体底部的整个平面或阵列上,极大地提高了单位面积内的I/O数量,适用于高引脚数、高性能芯片。

主要类型:

优点: 避免了BGA焊球带来的共面性问题,插座连接方便测试和更换(尤其对CPU)。

缺点: 插座会增加接触电阻和电感,成本也较高。

应用: 主要用于高性能CPU(如Intel, AMD桌面和服务器CPU)、高可靠性要求或需要频繁插拔的场合。

优点: I/O密度高,电气性能优异(引线短,电感小),散热性好(可通过底部焊球和基板导热),机械应力小(焊点位于封装下方)。

缺点: 焊点检查(需X光)、返修困难,对PCB设计和制造要求高。

变种:

PBGA (Plastic BGA): 塑料封装基板的BGA,最常见,成本较低。

CBGA (Ceramic BGA): 陶瓷封装基板的BGA,散热和可靠性更好,成本高。

TBGA (Tape BGA): 使用载带(Tape)作为基板的BGA。

FBGA (Fine-pitch BGA): 焊球间距更小的BGA(通常≤0.8mm),有时特指用于存储器的BGA(如DDR内存颗粒)。

LFBGA (Low-profile Fine-pitch BGA): 薄型精细间距BGA。

WLCSP (Wafer-Level Chip Scale Package): 晶圆级芯片尺寸封装。在晶圆上进行封装和植球,切割后几乎与裸芯片尺寸相同(CSP定义:封装尺寸≤1.2倍芯片尺寸)。是BGA的一种极致形态,成本低、尺寸最小、电性能最好,但封装体保护相对较弱。

BGA (Ball Grid Array): 球栅阵列封装。封装底部呈阵列式排布着焊球(Solder Ball)作为I/O接口。焊球间距通常≥0.8mm(常见1.0mm, 1.27mm, 0.8mm),也有更精细间距(0.5mm, 0.4mm)的变种。

LGA (Land Grid Array): 栅格阵列封装。封装底部是平面焊盘阵列(Land),而不是焊球。需要借助插座(Socket)使用,或者通过特殊的焊接工艺(如Intel CPU的SMT LGA)直接焊接到PCB上。插座提供可插拔性。

四、先进封装(Advanced Packaging)

特点: 超越了传统的单芯片单封装模式,致力于实现更高的集成度、更优的性能(带宽、延迟、功耗)、更小的尺寸和更低的系统成本。通常涉及将多个芯片(Die)集成在一个封装体内。

主要技术/类型:

代表: InFO(Integrated Fan-Out,台积电),广泛应用于移动处理器、网络芯片等。

Chiplet: 芯粒技术。将原本一个大型SoC的功能模块分解成多个更小、功能相对独立的“小芯片”(Chiplet),这些Chiplet可以采用不同的工艺节点制造(优化性能和成本),然后通过先进封装技术(如2.5D/3D、高密度基板)集成在一个封装内。这是当前高性能计算(CPU, GPU, AI加速器)领域的关键技术。

SiP (System in Package): 系统级封装。在一个封装外壳或基板内,集成多个具有不同功能的裸芯片(如处理器、存储器、RF、传感器等)以及可能的无源元件,形成一个功能完整的系统或子系统。集成方式可以是2D并排或3D堆叠。

2.5D IC: 将多个芯片并排放置在硅中介层(Silicon Interposer)上。中介层通过其内部的高密度布线(通常是硅通孔TSV和微凸块)实现芯片间的高速互连(带宽远超传统PCB布线),中介层再通过焊球连接到封装基板(如BGA)。典型代表是CoWoS(Chip on Wafer on Substrate)。

3D IC: 将多个芯片在垂直方向(Z方向)上直接堆叠并通过硅通孔(Through-Silicon Via, TSV)实现芯片间的垂直互连。能实现最短的互连路径、最高的带宽和最小的尺寸,但散热和制造复杂性是巨大挑战。

Fan-Out (扇出型封装): 在晶圆级封装(WLP)技术基础上发展而来。将芯片(Die)放置在重构晶圆上,通过模塑料(Molding Compound)包裹,然后在模塑料表面进行高密度布线(RDL - Redistribution Layer),将芯片的I/O触点“扇出”到更大的区域,形成焊球阵列。突破了芯片自身尺寸对I/O数量的限制,可以实现更高密度、更多I/O、更优的电热性能,且尺寸仍接近芯片级。

Embedded Die (嵌入式芯片): 将裸芯片直接嵌入到PCB或多层基板内部。可进一步减小系统厚度和尺寸,提高可靠性(芯片受保护更好)。

选择封装类型时考虑的关键因素

引脚数量/密度 (I/O Count/Pitch)

尺寸和外形限制 (Size/Form Factor)

性能要求 (电气性能:速度、噪声、功耗;热性能:散热需求)

可靠性要求 (工作环境、寿命)

成本 (封装成本、PCB制造成本、组装成本、测试成本)

制造和组装能力 (工厂设备、工艺水平)

可测试性和可返修性 (Testability/Reworkability)

供应链和可用性

IC封装技术是连接芯片微观世界与电子系统宏观世界的桥梁,其发展始终围绕着更小、更快、更强、更省、更可靠的目标。从DIP到SMT的QFP、QFN,再到高密度的BGA、LGA,直至推动半导体产业前沿的先进封装(SiP, 2.5D/3D, Chiplet, Fan-Out),封装形式的演进深刻地影响着电子产品的性能和形态。选择合适的封装是电子系统设计中至关重要的一环。