FT24C02A-Kxx EEPROM芯片产品简介:

FT24C02A是2048位串行电可擦除可编程只读存储器,通常称为EEPROM。它们被组织为256个字,每个字8位(1字节)。这些器件采用专有的先进CMOS工艺制造,适用于低功耗和低电压应用。这些器件有标准的8引脚DIP/SOP/TSSOP/MSOP/DFN/UDFN和5引脚SOT-23/TSOT-23封装。标准的2线串行接口用于处理所有读写功能。我们的扩展VCC范围(1.7V至5.5V)器件可实现广泛的应用。

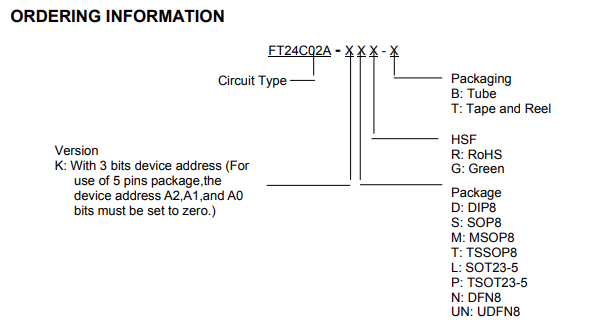

FT24C02A-Kxx产品型号:

FT24C02A-KDR-B;FT24C02A-KDG-B;FT24C02A-KSR-B;FT24C02A-KSR-T;FT24C02A-KSG-B;FT24C02A-KSG-T;FT24C02A-KMR-B;FT24C02A-KMR-T;FT24C02A-KMG-B;FT24C02A-KMG-T;FT24C02A-KTR-B;FT24C02A-KTR-T;FT24C02A-KTG-B;FT24C02A-KTG-T;FT24C02A-KNR-T;FT24C02A-KNG-T;FT24C02A-KUNR-T;FT24C02A-KUNG-T;FT24C02A-KLR-T*;FT24C02A-KLG-T*;FT24C02A-KPR-T*;FT24C02A-KPG-T*

FT24C02A-Kxx产品特点:

•低压和低功率操作:

FT24C02A:VCC=1.7V至5.5V。

•最大待机电流<1µA。

•16字节页面写入模式。

•允许部分页面写入操作。

•内部组织:256×8(2K)。

•标准2线双向串行接口。

•施密特触发器,用于噪声保护的滤波输入。

•自定时编程周期(最大5ms)。

•1 MHz(2.5-5V),400 kHz(1.8V)兼容性。

•写入操作前自动擦除。

•用于硬件数据保护的写保护引脚。

•高可靠性:通常可承受1000000次循环。

•数据保留100年。

•工业温度范围(-40℃至85℃)。

•标准8引脚DIP/SOP/TSSOP/MSOP/DFN/UDFN和5引脚SOT-23/TSOT-23无铅封装。

FT24C02A引脚说明

(A)串行时钟(SCL)该 SCL 输入的上升沿用于将数据锁存到 EEPROM(电可擦可编程只读存储器)器件中,而该时钟的下降沿则用于将数据从 EEPROM 器件中移出。

(B)串行数据线(SDA)SDA 数据线是串行器件的双向信号,属于开漏输出信号,可与其他开漏输出器件进行线或(wired-OR)连接。

(C)器件 / 片选地址(A2、A1、A0)这些是串行 EEPROM 器件的片选输入信号。通常,这些信号通过硬接线连接到高电平(VIH)或低电平(VIL)。若引脚悬空,器件内部会将其识别为低电平(VIL)。但由于客户应用中可能存在电容耦合问题,FMD(公司名,此处保留缩写)建议始终将地址引脚连接到确定的电平状态。若使用上拉或下拉电阻,FMD 建议采用 10 千欧(10kΩ)或更小阻值的电阻。

(D)写保护(WP)FT24C02A 系列器件配备 WP 引脚,用于保护整个 EEPROM 存储阵列免受编程操作影响。当 WP 引脚悬空或输入低电平(VIL)时,编程操作被允许;反之,若 WP 引脚连接到高电平(VIH)或电源电压(VCC),则所有编程功能被禁用。读操作不受 WP 引脚输入电平的影响。若 WP 引脚悬空,器件内部会将其识别为低电平(VIL)。但由于客户应用中可能存在电容耦合问题,FMD 建议始终将 WP 引脚连接到确定的电平状态。若使用上拉或下拉电阻,FMD 建议采用 10 千欧(10kΩ)或更小阻值的电阻。

存储结构

FT24C02A 器件包含 16 个页面。由于每个页面有 16 字节,因此对 FT24C02A 进行随机字寻址时,需要 8 位数据字地址。

器件操作

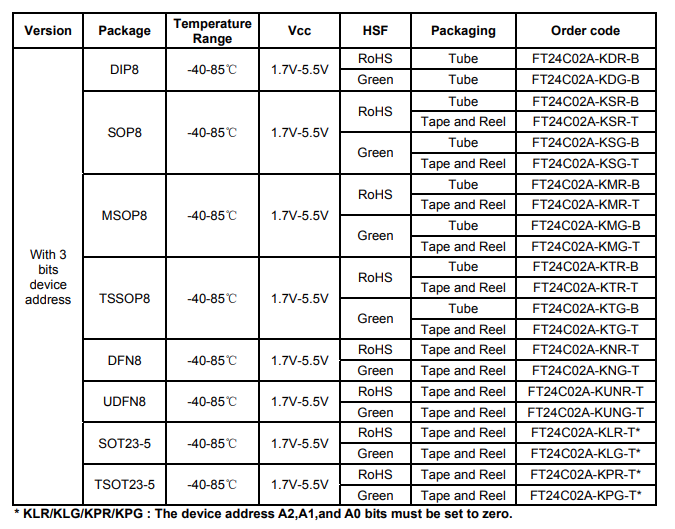

(A)串行时钟与数据跳变

SDA 引脚通常通过外部电阻上拉至高电平。仅当串行时钟(SCL)处于低电平(VIL)时,数据才允许发生变化。SDA 信号的任何跳变,都可能被解读为下述的起始条件(START condition)或停止条件(STOP condition)。

(B)起始条件(START condition)

当 SCL≥高电平(VIH)时,SDA 信号从高电平跳变至低电平,此过程被解读为起始条件。所有有效的命令都必须以起始条件开头。

(C)停止条件(STOP condition)

当 SCL≥高电平(VIH)时,SDA 信号从低电平跳变至高电平,此过程被解读为停止条件。所有有效的读命令或写命令都以停止条件结尾。若该停止条件出现在读命令之后,器件将进入待机模式(STANDBY mode);若该停止条件出现在页写或字节写命令之后,器件会在自定时内部编程完成后,触发进入待机模式。

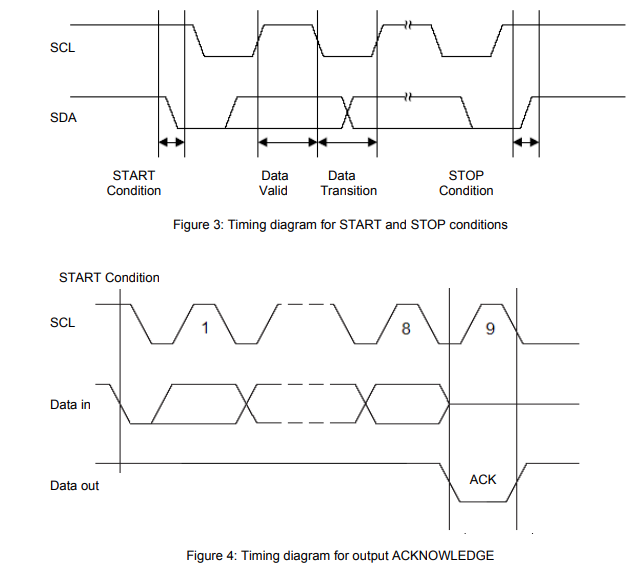

(D)应答(ACKNOWLEDGE)

二线制协议以 8 位字的形式,与 EEPROM 之间传输地址和数据。EEPROM 在接收到每个字后,会输出一个 “0” 来对应答数据或地址进行确认。应答信号会在每个字传输后的第 9 个串行时钟周期内产生。

(E)待机模式(STANDBY mode)

在以下场景下,EEPROM 会进入低功耗待机模式:刚上电后、在读模式下接收到停止位(STOP bit)后、或完成自定时内部编程操作后。

(F)软复位(SOFT RESET)

当协议中断(如掉电)或系统复位后,可通过以下步骤对任意二线制器件进行复位:

产生一个起始条件;

时钟输出 18 个 “1” 数据位;

在 SDA 处于高电平时,产生一个起始条件。

器件寻址(DEVICE ADDRESSING)

二线制串行总线协议规定,在起始位(START bit)条件之后,需发送一个 8 位的器件地址字,以触发有效的读命令或写命令。器件地址的前 4 位最高有效位必须为 “1010”,这是所有串行 EEPROM 器件的通用地址前缀。接下来的 3 位是器件地址位,这 3 位器件地址位(第 5 位、第 6 位、第 7 位)需与外部片选 / 地址引脚的状态相匹配。若匹配成功,EEPROM 器件会在第 8 位读 / 写位传输完成后输出一个应答(ACKNOWLEDGE)信号;若不匹配,器件将进入待机模式(STANDBY mode)。

地址字的最后 1 位(即第 8 位)为读 / 写命令位。若第 8 位为高电平(VIH),器件将进入读模式;若检测到第 8 位为 “0”,器件则进入编程模式。

写操作(WRITE OPERATIONS)

(A)字节写(BYTE WRITE)

字节写操作的流程如下:

微控制器发送起始位(START bit)条件;

接着发送有效的 EEPROM 器件地址及写命令;

若器件地址位与片选地址匹配,EEPROM 会在第 9 个时钟周期发送应答信号;

随后微控制器发送剩余的 8 位低字节字地址,EEPROM 会在第 18 个时钟周期对该 8 位地址字发送应答信号;

微控制器继续传输 8 位数据,在第 27 个时钟周期接收到 EEPROM 的应答信号后,微控制器发送停止位(STOP bit);

EEPROM 接收到停止位后,将进入自定时编程模式,此模式下所有外部输入均被禁用;

经过编程时间 TWC 后,字节编程完成,EEPROM 器件恢复至待机模式。

(B)页写(PAGE WRITE)

页写操作与字节写操作类似,核心区别在于:页写可在同一页面(或存储行)内对 1 至 16 字节的数据进行编程(FT24C02A 的存储结构为每页面 / 存储行含 16 字节)。

页写操作的具体流程如下:

与字节写操作相同,微控制器先发送写命令、器件地址及字地址,并接收 EEPROM 的应答信号;

微控制器发送第 1 个 8 位数据字节,在第 27 个时钟周期接收到 EEPROM 的应答信号后,不发送停止位;

反之,微控制器继续发送第 2 个 8 位数据字节,EEPROM 会在第 36 个时钟周期发送应答信号;

上述 “数据发送 - EEPROM 应答” 的周期会重复进行,直至微控制器在第 n×9 个时钟周期后发送停止位;

停止位发送后,EEPROM 进入自定时的部分页或全页编程模式;

经过编程时间 TWC 后,页编程完成,器件恢复至待机模式。

页写操作的地址规则:

字地址的低 4 位(列地址)在每接收一个数据字节后,会在内部自动加 1;

字地址的其余位(行地址)在内部保持不变,始终指向待编程的特定存储行 / 页面;

页写的第一个数据字节可对应任意列地址,同一页面内最多可加载 16 个数据字节;

若加载的数据字节数超过 16 个,第 17 个数据字节会覆盖第 1 个数据字节的列地址,第 18 个数据字节覆盖第 2 个数据字节的列地址,以此类推(即列地址会 “循环覆盖” 之前已加载的数据)。

(C)应答轮询(ACKNOWLEDGE POLLING)

应答轮询可用于在自定时内部编程过程中,查询器件的编程状态,具体机制如下:

向 EEPROM 发送有效的读或写地址命令:

若器件仍处于自定时编程模式,将不会在第 9 个时钟周期发送应答信号;

若编程已完成且器件已恢复至待机模式,则会在第 9 个时钟周期返回有效的应答信号。

读操作(READ OPERATIONS)

读命令与写命令的流程类似,核心区别在于:地址字的第 8 位(读 / 写位)需设为 “1”。读操作包含三种模式,具体如下:

(A)当前地址读(CURRENT ADDRESS READ)

在器件电源未断开的情况下,EEPROM 内部的地址字计数器会保持 “上一次读 / 写地址 + 1” 的值。当前地址读操作的流程如下:

微控制器发送起始位(START bit),并发送有效的器件地址字(第 8 位读 / 写位设为 “1”);

EEPROM 在第 9 个串行时钟周期发送应答信号;

随后 EEPROM 会串行移出一个 8 位数据字节,内部地址字计数器自动加 1;

对于当前地址读模式,微控制器不会在第 18 个时钟周期发送应答信号,而是在第 18 个时钟周期后发送有效的停止位,终止读操作;

操作结束后,器件恢复至待机模式。

(B)连续读(SEQUENTIAL READ)

连续读操作与当前地址读操作非常相似,关键差异在于微控制器可通过发送应答信号,持续获取后续数据,具体流程如下:

微控制器发送起始位及有效的器件地址字(第 8 位读 / 写位设为 “1”);

EEPROM 在第 9 个串行时钟周期发送应答信号,并串行移出一个 8 位数据字节,同时内部地址字计数器自动加 1;

与当前地址读不同,微控制器会在第 18 个时钟周期发送应答信号,告知 EEPROM 需继续输出下一个数据字节;

EEPROM 接收到应答信号后,会根据已递增的内部地址计数器,串行移出下一个 8 位数据字节;

若微控制器需继续读取数据,会在第 27 个时钟周期再次发送应答信号,重复上述数据传输过程;

当内部地址计数器达到最大有效地址时,会循环回存储阵列的起始地址;

若需终止连续读操作,微控制器只需对最后一个接收的数据字节不发送应答信号,转而发送停止位即可,之后器件恢复至待机模式。

(C)随机读(RANDOM READ)

随机读操作分为两步:第一步通过 “伪写”(dummy write)指令,将目标读地址初始化到内部地址计数器;第二步执行当前地址读操作,具体流程如下:

第一步:初始化目标读地址

微控制器先发送起始位;

接着发送有效的器件地址(第 8 位读 / 写位设为 “0”,即伪写命令);

EEPROM 发送应答信号;

微控制器发送目标读地址,EEPROM 再次发送应答信号。

第二步:执行当前地址读

微控制器无需向 EEPROM 发送实际写数据,而是直接执行当前地址读指令以读取目标地址的数据;

注意:一旦微控制器发送新的起始位,EEPROM 会重置内部编程过程,并执行新的指令(即当前地址读指令)。