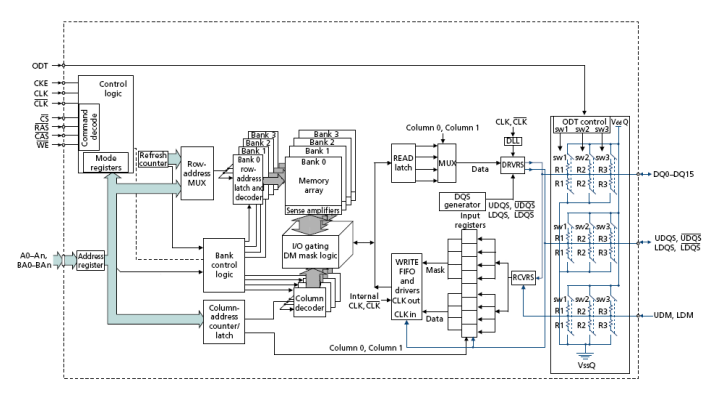

M14D2561616A(2C) 4M x 16 Bit x 4 Banks DDR II SDRAM

M14D2561616A-21.5BG2C特征

JEDEC标准

VDD=1.8V±0.1V,VDDQ=1.8V?.1V

内部流水线双数据速率架构;每个时钟周期两次数据访问

双向差分数据选通(DQS、DQS);

DQS

可以禁用单端数据选通操作。

片上DLL

差分时钟输入(CLK和CLK)

DLL将DQ和DQS转换与CLK转换对齐

1KB页面大小

-行地址:A0至A12

-列地址:A0至A8

四方银行业务

CAS延迟:3、4、5、6、7、8、9

加性延迟:0、1、2、3、4、5、6、7

突发类型:顺序和交错

爆裂长度:4,8

除数据和DM外的所有输入都在系统时钟(CLK)的上升沿采样

数据选通(DQS)两侧的数据I/O转换

DQS与READ数据边缘对齐;中心与WRITE数据对齐

数据掩码(DM)仅用于写掩码

片外驱动器(OCD)阻抗调整

提高信号质量的管芯端接

特殊功能支持

-50/75/150欧姆ODT

-高温自刷新率启用

-DCC(占空比校正器)

-部分阵列自刷新(PASR)

自动和自刷新

刷新周期:

-0℃≤TC≤+85℃时8192个周期/64ms(7.8μs刷新间隔)

-+85℃<TC≤+95℃时8192个周期/32ms(3.9μs刷新间隔)

SSTL_18接口

如果tCK<1.875ns,则设备无法支持带自动预充电功能的写入。

Data Rate(CL-tRCD-tRP):

DDR2-1333 (9-10-10)