F50L1G41XA (2B) 3.3V 1Gbit SPI NAND Flash Memory

ESMT(晶豪科技)F50L1G41XA-104YG2BE SPI NAND Flash存储芯片特征

单层电池(SLC)技术

组织

-页面大小x1:2176字节(2048+128字节)

-块大小:64页(128K+8K字节)

-设备大小:1Gb(1个平面,每个平面1024个块)

标准和扩展SPI兼容串行总线

界面

-指令,地址在1个引脚上;数据输出在1、2或4个引脚上

-1针上的说明;地址,数据输出在2或4个引脚上

-指令,地址在1个引脚上;数据输入在1或4个引脚上

支持用户可选的内部ECC

-8位/扇区

阵列性能

-104 MHz时钟频率(最大)

-页面读取:25μs(MAX),管芯ECC禁用;70μs

(MAX)启用了管芯ECC

-页面程序:200μs(TYP),管芯ECC禁用;

220μs(TYP),启用片上ECC

-块擦除:2ms(TYP)

高级功能

-读取页面缓存模式

-读取唯一ID

-读取参数页面

设备初始化

-通电后自动设备初始化

安全

-第一块在出厂时有效

启用ECC

-带锁寄存器的软件写保护

-硬件写保护以冻结BP位

-锁紧以在一次电源循环中冻结BP钻头

永久性闭锁保护

-OTP空间:10页一次性可编程

NAND闪存区

工作电压范围

-VCC=2.7–3.6V

工作温度

-商用:0°C至+70°C

质量和可靠性

-耐久性:100000个程序/擦除周期

-数据保留:符合JESD47H标准;

见资格报告

-附加:非循环数据保留:10年24/7@70°C

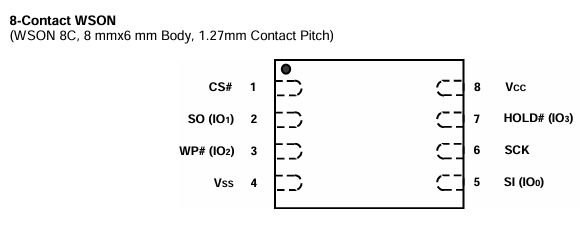

封装:8-contact WSON (without expose metal pad)

F50L1G41XA-104YG2BE SPI NAND Flash存储芯片一般说明

串行外围接口(SPI)NAND是一种SLC NAND闪存设备,提供经济高效的非易失性存储器必须将引脚数保持在最低限度的存储解决方案。它也是SPI NOR的替代解决方案,提供卓越的写入性能SPI NOR的性能和每比特成本。硬件接口创建了一个低引脚的设备,其标准引脚仍然存在从一种密度到另一种密度都是一样的,并且支持未来升级到更高的密度,而无需重新设计电路板。

串行电气接口遵循行业标准串行外围接口。新的命令协议和寄存器为SPI操作定义。该命令集类似于常见的SPI-NOR命令集,经过修改以处理NAND特定的功能以及其他新功能。

新功能包括用户可选择的内部ECC和通电时的首页自动加载。SPI NAND闪存设备有六条信号线加上VCC和地(GND)。信号线包括SCK(串行时钟)、SI、SO(用于命令/响应和数据输入/输出)和控制信号CS、HOLD#、WP#。此硬件接口创建了一个具有标准引脚的低引脚数设备,与从一个密度到另一个密度,支持未来升级到更高的密度,而无需重新设计电路板。

串行NAND闪存设备的每个块被划分为64个可编程页,每个页由2176个字节组成。每一页都是进一步划分为2048字节的数据存储区和128字节的备用区。128字节的区域通常用于存储和

错误管理功能。

通电后默认启用内部ECC,当页面写入内存核心时,会在内部生成ECC代码。

ECC码存储在每页的备用区域中。当页面被读取到缓存寄存器时,ECC码会再次计算并与存储的值进行比较。必要时纠正错误。设备要么输出校正后的数据,要么返回ECC错误状态。设备初始化后,可以关闭内部ECC。如果要求ECC在以下情况下关闭,则代表打开电源。

第一块在出厂时有效。还提供安全功能,包括软件块保护:锁紧硬件保护模式可避免阵列数据损坏。

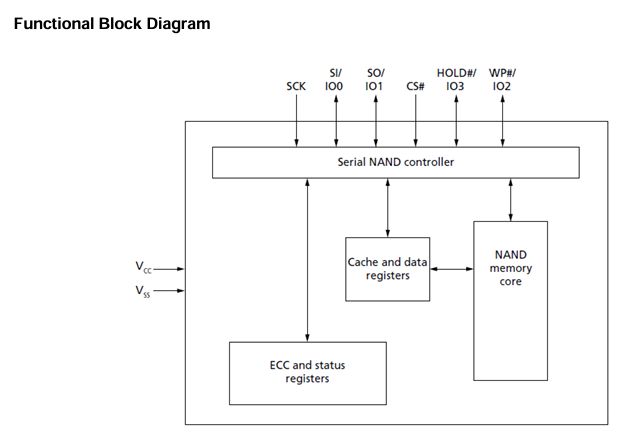

F50L1G41XA-104YG2BE结构

这些设备使用按页/块组织的行业标准NAND闪存核心。标准并行NAND闪存SPI接口取代了电气接口和I/O逻辑。新的命令协议集是SPI NOR的修改业界可用的命令集。这些修改专门用于处理与NAND闪存架构相关的功能。这个界面支持页面和随机读/写以及内部数据移动功能。该设备还包括内部ECC功能。

数据逐页传输到NAND闪存阵列或从NAND闪存阵列传输到缓存寄存器和数据寄存器。缓存寄存器最接近I/O控制电路,并充当I/O数据的数据缓冲器;数据寄存器最接近存储器阵列,并充当用于NAND闪存阵列操作的数据缓冲器。

NAND闪存阵列在基于页的操作中被编程和读取;它在基于块的操作中被擦除。缓存寄存器用作缓冲存储器,以实现随机数据读/写操作。这些设备还使用新的SPI状态报告设备操作状态的寄存器。