F50L1G41LB (2M) 3.3V 1 Gbit SPI NAND Flash Memory

ESMT(晶豪科技)F50L1G41LB-104YG2M SPI NAND Flash芯片特征

电源电压:3.3V(2.7V~3.6V)

组织

-存储单元阵列:(128M+4M)x 8位

-数据寄存器:(2K+64)x 8位

自动编程和擦除

-页面程序:(2K+64)字节

-块擦除:(128K+4K)字节

页面读取操作

-页面大小:(2K+64)字节

-从Cell读取以向内部ECC注册:100us

存储单元:1bit/存储单元

支持SPI模式0和SPI模式31

快速写入周期时间

-编程时间:400us

-块擦除时间:4ms

硬件数据保护

-电源转换期间的编程/擦除锁定

可靠的CMOS浮栅技术

-内部ECC要求:1bit/512Byte

-耐久性:100K编程/擦除周期

-数据保留期:10年

命令注册操作

NOP:4个周期

OTP操作

坏块保护

开机读取

注:1。模式0:CPOL=0,CPHA=0;模式3:CPOL=1,CPHA=1

工作温度:0°C~+70°C

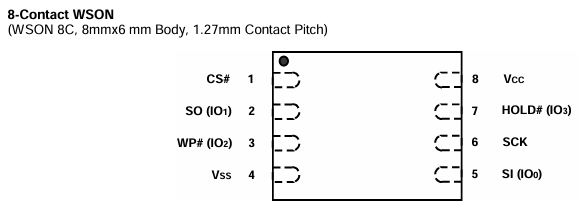

封装:8-contact WSON (without expose metal pad)

| 参数(Parameters) | 参数值(Values) | 专业释义 |

| Vcc | 3.3V | 电源电压 |

| Width | x1, x2¹, x4 | 数据位宽(单通道 / 双通道 / 四通道) |

| Frequency | 104MHz | 工作频率 |

| Internal ECC Correction | 1-bit | 内置 ECC 纠错能力(1 位纠错) |

| Transfer Rate | 9.6ns | 传输速率(周期时间) |

| Loading Throughput | 104MT/s | 加载吞吐量(1.04 亿次 / 秒) |

| Power-up Ready Time | 1ms (maximum value) | 上电就绪时间(最大值) |

| Max Reset Busy Time | 1ms (maximum value) | 最大复位忙时间(最大值) |

F50L1G41LB-104YG2M SPI NAND Flash芯片一般说明

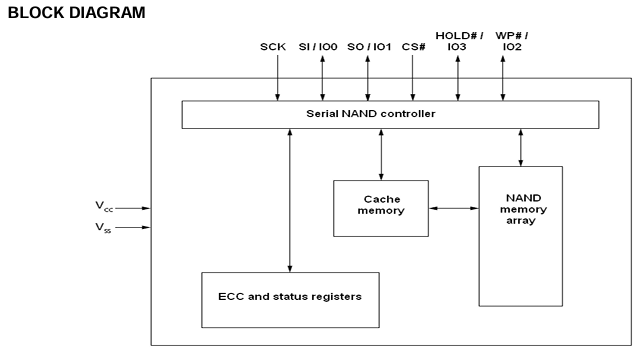

串行电气接口遵循行业标准串行外围接口(SPI),提供经济高效的非易失性引脚数必须为的系统中的内存存储解决方案保持在最低限度。该设备是1Gb SLC SPI-NAND闪存基于标准并行NAND闪存的存储设备,但为SPI定义了新的命令协议和寄存器操作。它也是SPI-NOR的替代品,提供卓越的通过SPI-NOR实现写入性能和每比特成本。 该命令集类似于常见的SPI-NOR命令集,修改以处理NAND特定功能和新特性。 新功能包括用户可选择的内部ECC。与内部ECC已启用,当页面处于以下状态时,ECC代码会在内部生成写入存储器阵列。ECC码存储在每页的空白区域。当页面被读取到缓存时再次计算ECC码并与存储的值。必要时纠正错误。设备输出已纠正的数据或返回ECC错误状态。 内存被划分为可以擦除的块独立地,因此可以在旧数据时保留有效数据数据被擦除。该设备包含1024个块,由以下部分组成64页,由32系列的两个NAND结构组成连接的闪存单元。每页包含2112字节进一步划分为2048字节的数据存储区域单独的64字节备用区域。通常使用64字节区域用于内存和错误管理。 引脚用作信号端口。该设备有六个信号线加VCC和地(GND、VSS)。信号线为SCK(串行时钟)、SI(命令和数据输入)、SO(响应和数据输出)和控制信号CS#、HOLD#、WP#。