F59D2G81XA(2B) 2 Gbit (256M x 8) 1.8V NAND Flash Memory

ESMT(晶豪科技) F59D2G81XA-45BG2B SLC NAND Flash存储芯片特点:

供电电压:1.8V(1.7V~1.95V)

符合开放式 NAND 闪存接口(ONFI)1.0 标准

采用单层单元(SLC)技术

存储结构

页大小:2176 字节(2048 + 128 字节)

块大小:64 页(128K + 8K 字节)

平面大小:2 个平面,每平面 1024 个块

器件总容量:2048 个块

异步 I/O 性能

读周期 / 写周期时间(tRC/tWC):30ns

阵列操作性能

页读取:30μs

页编程:典型值 200μs

块擦除:典型值 2ms

命令集:遵循 ONFI NAND 闪存协议

高级命令集

页编程缓存模式

页读取缓存模式

一次性可编程(OTP)模式

可编程驱动强度

双平面命令(仅在关闭 ECC 时可用)

读取唯一 ID

内部数据搬移

操作状态字节(软件方式)

可检测:

操作完成状态

操作成功 / 失败状态

写保护状态

就绪 / 忙信号(R/B#)(硬件方式)

用于检测操作完成

WP#:对整个器件进行写保护

出厂时块 0 带 ECC 校验有效。

最小所需 ECC 要求参见错误管理相关说明。

上电后第一条命令必须为复位命令(FFh)

支持在读取数据所在平面内执行内部数据搬移操作

质量与可靠性

数据保存:符合 JESD47G 标准

擦写寿命:100,000 次编程 / 擦除周期

额外特性:未循环数据保存时间:10 年

工作温度

商用级:0℃~+70℃

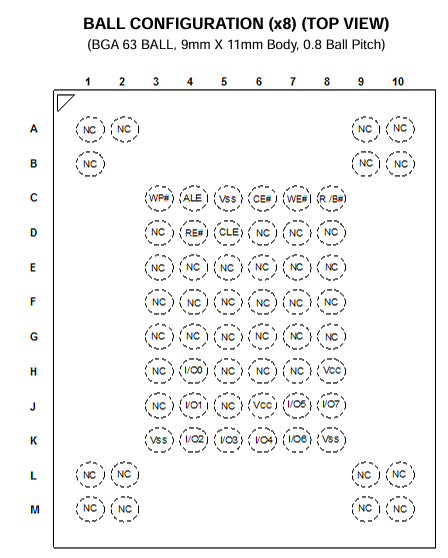

封装:63 ball BGA

F59D2G81XA-45BG2B SLC NAND Flash存储芯片说明:

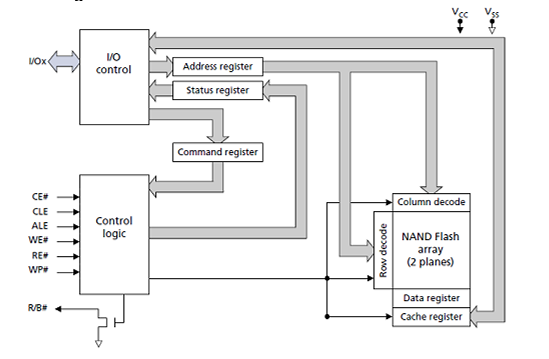

NAND闪存器件包含用于高性能 I/O 操作的异步数据接口。这类器件采用高度复用的8位总线(I/Ox)来传输命令、地址和数据。实现异步数据接口共使用5个控制信号:CE#、CLE、ALE、WE# 和 RE#。另有额外信号用于硬件写保护控制以及器件状态监测(R/B#)。

该硬件接口使器件引脚数量较少,并采用标准引脚排布,且不同存储密度的器件引脚定义保持一致,便于后续升级至更高密度时无需重新设计电路板。

Target(目标单元) 是由芯片使能信号访问的内存单元,一个目标单元包含一个或多个NAND闪存裸片(Die)。NAND闪存裸片是可独立执行命令并反馈状态的最小单元,在ONFI规范中,该裸片被称为逻辑单元(LUN)。每个芯片使能信号至少对应一个NAND闪存裸片。更多细节请参见《器件与阵列结构》章节。