M55D4G16256A(2R) 32M x 16 Bit x 8 Banks LPDDR3 SDRAM

ESMT(晶豪科技)M55D4G16256A-CDBG2R特征:

超低压核心和I/O电源

VDD1=1.70 ow-vol

VDD2、VDDCA、VDDQ=1.14ow-vol

组织

32M字x16位x8个存储体

符合JEDEC LPDDR3标准

4KB页面大小

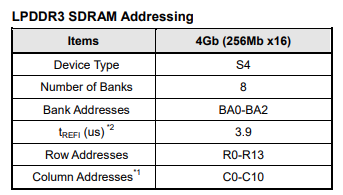

行地址:R0到R13

列地址:C0至C10(x16位)

每次突发访问的自动预充电选项

八位预取DDR架构

八家内部银行同时运营

双倍数据速率,命令/地址输入;

在每个CK边上输入的命令

每字节数据的双向/差分数据选通(DQS)

差分时钟输入(CK_t和CK_c)

用于写入数据的数据掩码(DM)

CA输入定时的命令/地址(CA)培训

调整

时钟到DQ、DQS和DM定时的写均衡

调整

接口:HSUL-12

读取延迟(RL):3、6、8、9、10、11、12、14、16

爆破长度(BL):8

突发类型(BT):顺序

每个银行刷新以进行并发操作

自动温度补偿自刷新(ATCSR)

自动刷新和自刷新

刷新周期:8192个周期/32ms

平均刷新周期:3.9μs

部分阵列自刷新(PASR)

银行屏蔽

分段屏蔽

深度断电(DPD)

可编程驱动强度(DS)

模内终止(ODT)

封装:178 Ball BGA;

Max Freq:800MHz

Data Rate (Mb/s/pin):1600

1.最低有效列地址C0不在CA总线上传输,并且暗示为零。

2.所有气缸组刷新的tREFI值均在温度规格范围内(TCASE<=85℃)。

3.CA总线上未使用的行和列地址值为“不在乎”

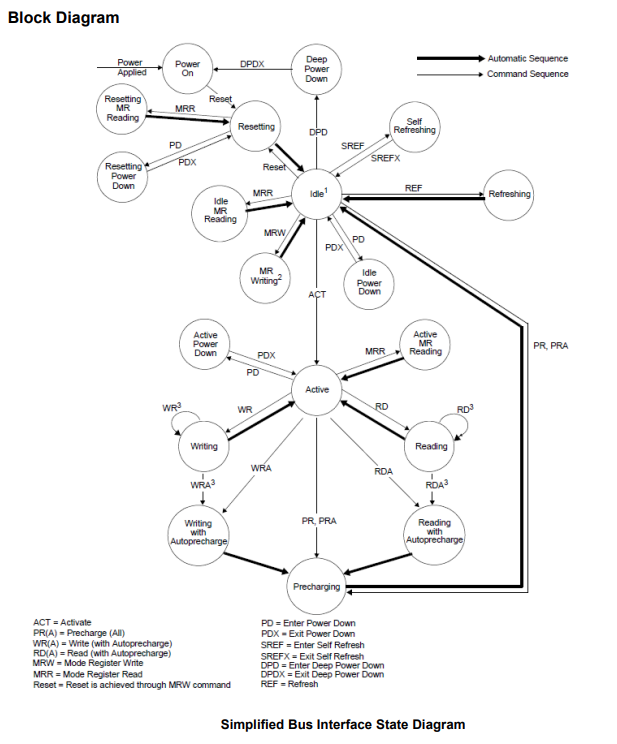

1.在空闲状态下,所有银行都已预充电。

2.在MRW进入CA训练模式或写入水平模式的情况下,状态机不会自动返回空闲状态。在这些情况下,需要额外的MRW命令来退出任一操作模式并返回空闲状态国家。请参阅“CA培训”或“写作水平”部分。

3.不允许终止脉冲。对于这些状态转换,必须在转换之前完成突发操作可能发生。

4.小心使用此图。它旨在提供可能的状态转换和控制命令的平面图他们,不是所有的细节。特别是,涉及多家银行的情况没有得到充分详细的记录。